Alveo U55C/U50/U280 数据中心加速器卡修改SI5394输出时钟配置服务

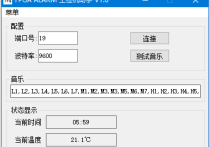

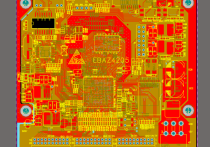

加速卡板载有SI5394,可以输出不同的时钟频率。用于不同的用途,例如万兆以太网等:

本站提供SI5394修改OUT0和OUT1频率的付费服务,支持但不限于156.25Mhz等,能够固化写入,断电后不丢失。

如片内NVM超过写入次数限制,也支持更换硬件芯片,或提供新的黄金工程。

邮寄修改服务,3工作日内完成,每个板卡配置费用4000元(含税)。

所有工程及操作教程 23888元(含税)。

支持开票,也支持更多相关功能开发,合作可以邮件联系:chenyu@myfpga.cn