3-8译码器

译码:译码是编码的逆过程,在编码时,每一种二进制的代码,都赋予了特殊的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。

译码器:一类多输入多输出的组合逻辑电路器件,其可以分为:变量译码和显示译码两类

3-8译码器 模块框图:

输出信号定义为 8位宽

译码器真值表:

译码器波形图:

代码部分:

选择器代码:在Src文件夹中新建 deocder.v文件

module decoder

(

input wire in_1,

input wire in_2,

input wire in_3,

output reg [7:0] out

);

always@(*)

case({in_1,in_2,in_3})

3'b000: out = 8'b0000_0001;

3'b001: out = 8'b0000_0010;

3'b010: out = 8'b0000_0100;

3'b011: out = 8'b0000_1000;

3'b100: out = 8'b0001_0000;

3'b101: out = 8'b0010_0000;

3'b110: out = 8'b0100_0000;

3'b111: out = 8'b1000_0000;

default: out = 8'b0000_0001;

endcase

endmodule仿真文件代码:在Sim文件夹中新建 tb_decoder.v 文件

`timescale 1ns/1ns

module tb_decoder();

reg in_1 ;

reg in_2 ;

reg in_3 ;

wire [7:0] out ;

initial

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

in_3 <= 1'b0;

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

always #10 in_3 <= {$random} % 2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1=%b,in_2=%b,in_3=%b,out=%b",$time,in_1,in_2,in_3,out);

end

decoder decoder_inst

(

.in_1(in_1),

.in_2(in_2),

.in_3(in_3),

.out (out)

);

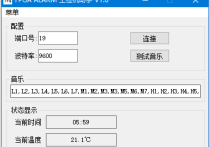

endmodule结果:

打印的日志和真值表中相对应

波形也正常