自研板卡 Xilinx A7 100Msps/8bit/2CH ADC WithTrig 千兆以太网 40MBW

1板卡设计框图

1.1电源

板卡支持DC和Type-C供电两种方式,5V电源通过多个LDO产生数字和模拟用的多路3.3V电源以及-5V运放用电源

1.2模拟输入

设计带宽为40Mhz。

1.3触发输入

1.4数字部分

2.测试记录

2.1电源功率

测试多路电源电压正常,纹波<1%,满足设计目标。

实测无FPGA情况下整板功率0.59W,带FPGA整板正常模式功率2.5W,全速以太网发送时功率2.9W,满足设计目标。

2.2输入测试

ADC输入波形无明显失真,幅值同仿真结果基本一致。

在预设电压范围内实测-3dB带宽范围为43Mhz,同仿真结果基本一致。

2.3以太网通信测试

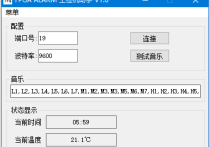

2.4上位机显示测试