Intel FPGA初级考试模拟试题 四套含答案

*1.下列对异步信号进行同步的描述错误的是(使用锁存器)。

采用保持寄存器加握手信号的方法

特殊的具体应用电路结构,根据应用的不同而不同

使用锁存器

异步 FIFO

*2.FPGA 的可编程是主要基于什么结构(查找表(LUT))。

查找表(LUT)

ROM 可编程

PAL 可编程

与或阵列可编程

解析:

FPGA基于查找表结构和SRAM CMOS工艺,集成度高、速度快、成本低;

CPLD基于乘积项结构和EECMOS工艺,与FPGA相比,集成度稍低一些,相同规模下成本略高。

*3.对时钟约束“create_clock -name clk100 -period 10 -waveform {0.00 5.00} [get_ports ClkIn]”的表述不正确的是(0到5ns期间为不定态)。

周期为10ns

0到5ns期间为不定态

占空比为50%

时钟信号名称为“clk100 ”

*4.下列哪些语句不可以被综合成电路(initial)。

initial

always

assign

For

解析:

(1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)(3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

*5.片上可编程器件的英文缩写是(SOPC)。

SOP

SOPC System On a Programmable Chip

SOC System on Chip

SPI

*6.下列关于同步和异步复位描述正确的是(同步复位需要在时钟沿来临的时候才会对整个系统进行复位)。

同步复位是不受时钟影响(异步复位:不受时钟影响)

使用FPGA设计时芯片的异步复位和同步复位可随意替换使用

同步复位需要在时钟沿来临的时候才会对整个系统进行复位

同步复位最大的优点是, 数据通路可以不依赖于时钟而复位可用

解析:

同步复位在时钟沿才复位信号,完成复位动作。异步复位不管时钟,只要复位信号满足条件,就完成复位动作。异步复位对复位信号要求比较高,不能有毛刺,如果其与时钟关系不确定,也可能出现亚稳态。

异步复位是不受时钟影响的,需要一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。使用FPGA 设计时芯片的异步复位必须要走全局网络。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。然而, 异步复位 STA (静态时序分析) 的复杂性要高于同步复位设计; 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

*7.一个四位十六个状态的格雷码计数器,起始值为1001,经过100个时钟脉冲作用之后的值为(0011)。

0101

0011

0110

0000

解析:https://blog.csdn.net/Reborn_Lee/article/details/98242445

*8.下列关于亚稳态描述错误的是(异步FIFO不能用于解决亚稳态问题)。

电路处于中间状态的时间变长,使得电路“反应”迟钝的现象,叫做亚稳态

对于单比特控制信号采用二级触发器缓冲,可以几乎消除亚稳态

对于多比特数据可以采用握手的方式来消除亚稳态

异步FIFO不能用于解决亚稳态问题

解析:

什么叫亚稳态?如何解决亚稳态。

由于建立时间或者保持时间不满足而导致触发器需要花很长时间来实现输出逻辑达到标准电平,也就是说电路处于中间状态的时间变长,使得电路“反应”迟钝的现象,叫做亚稳态。

例如输入信号在时钟有效沿的建立时间与保持时间之间改变了,导致不满足触发器的建立时间和保持时间,导致输出有一段时间的不稳定态,就是亚稳态。

解决亚稳态的办法很多,需要具体情况具体分析:

例如,对于单比特控制信号从慢时钟到快时钟域同步,需要采用二级触发器缓冲,可以几乎消除亚稳态。

对于多比特数据从慢时钟域到快时钟域的传输,我们可以采用握手的方式来消除亚稳态。

而异步FIFO可以解决所有亚稳态问题,几乎通吃。无论是从慢时钟到快时钟域还是从快时钟域到慢时钟域的信号传输,我们都可以采用异步FIFO的方式来解决亚稳态。

对于复位信号,可以采用异步复位,同步撤离的方式来解决亚稳态。

*9.关于FPGA芯片内存储器资源描述错误的是(使用BLOCK RAM资源需占用额外的逻辑资源,并且速度慢)。

FPGA内部有BLOCK RAM存储器

使用BLOCK RAM资源需占用额外的逻辑资源,并且速度慢

BLOCK RAM由一定数量固定大小的存储块构成的

FPGA内部有由LUT配置成的分布式存储器

解析:

FPGA 芯片内有两种存储器资源:一种叫 block ram,另一种是由 LUT 配置成的内部存储器(也就是分布式 ram)。Block ram 由一定数量固定大小的存储块构成的,使用 BLOCK RAM资源不占用额外的逻辑资源,并且速度快。但是使用的时候消耗的 BLOCK RAM 资源是其块大小的整数倍

*10.INTEL FPGA芯片不包括(Kintex-7)。

Cyclone V

Kintex-7

Arria

Stratix

*11.关于Quartus软件产生的编程文件描述错误的是(MCS文件也可用于Quartus编程)。

sof 是SRAM Object File ,下载到FPGA 中,断电丢失

MCS文件也可用于Quartus编程

FPGA 工程最终生产两种不同用途的文件,它们分别是.sof 和.pof

pof 是Programmer Object File,下载到配置芯片中,上电重新配置FPGA

*12.IP 核在EDA 技术和开发中占有很重要的地位,提供VHDL 硬件描述语言功能块,但不涉及实现该功能模块的具体电路的IP 核为(软件IP)。

硬件IP

固件IP

软件IP

都不是

*13.大规模可编程器件主要有CPLD 和FPGA 两类,下面对FPGA 结构与工作原理描述中,正确的是(基于SRAM 的FPGA 器件,每次上电后必须进行一次配置)。

FPGA 全称为复杂可编程逻辑器件

FPGA 是基于哈佛结构的可编程逻辑器件

基于SRAM 的FPGA 器件,每次上电后必须进行一次配置

在Intel公司生产的器件中, MAX7000 系列属于FPGA结构

*14.大规模可编程器件主要有CPLD 和FPGA 两类,其中CPLD 通过(可编程乘积项逻辑)实现其逻辑功能。

输入缓冲

可编程乘积项逻辑

查找表(LUT)

输出缓冲

*15.下列不属于Verilog HDL中的循环语句是(jump)。

jump

for

while

Repeat

解析:

Verilog 循环语句有 4 种类型,分别是 while,for,repeat,和 forever 循环。循环语句只能在 always 或 initial 块中使用,但可以包含延迟表达式。

*16.如果网线型变量说明后未使用,那么其缺省值为(z)。

0

1

x

Z

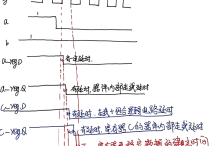

*17.下面程序段的运行结果不正确的是(70 r=0)。

`timescale 10ns/1ns

fork

#20 r=1’b 0;

#10 r=1’b 1;

#15 r=1’b 1;

#25 r=1’b 1;

#5 r=1’b 0;

join

initial $monitor($time ,,,”r=%b”,r );

Endmodule

0 r=x

45 r=1

70 r=0

20 r=0

*18.实现下列结果正确表达式为(assign out=sel? in1:in0)。

assign out=sel&& in1&&in0

assign out=sel? in1:in0

assign out=sel||in1||in0

assign out=sel|| in1&&in0

*19.在一组格雷码中,任意相邻的两组编码之间只有一位不同,常用于通信系统。二进制编码转化为格雷码编码的步骤是:格雷码最高位与二进制码相同;格雷码第i位等于二进制码的第i与第i+1位异或。补充完整下列9位二进制码转9位格雷码编码器。 答案:AC

module Bin2Gray #(

parameter PTR = ( 1 )

) (

input wire [PTR : 0] Bin,

output wire [PTR : 0] Gray

);

assign Gray[PTR] = Bin[PTR];

generate

( 2 ) i;

for( i = 0; i < PTR; i++ ) begin

assign Gray[i] = Bin[i] ^ Bin[i+1];

end

endgenerate

endmodule

请在下面选择正确的答案组合

(1) A.8 B.7 C.9 D.10

(2) A.int B.real C.genvar D.char

(1).B (2).C

(1).D (2).A

(1).A (2).C

(1).C (2).D

*20.关于锁存器(latch)和触发器(flip-flop)的描述错误的是(锁存器为边缘敏感)。

电平敏感的存储器件称为锁存器

锁存器可分为高电平锁存器和低电平锁存器

触发器是有交叉耦合的门构成的双稳态的存储原件

锁存器为边缘敏感

*21.Intel FPGA都有以下哪几个系列(全部)。 【多选题】

Stratix

Cyclone

Arria

AgileX

*22.Cyclone V SoC FPGA里有以下哪些资源(全部)。 【多选题】

HPS(Hard Process System)

LAB

时钟资源

IOB

*23.以下哪些是组合逻辑电路中常见的逻辑门(异或门 与门 与非门)。 【多选题】

异或门

与门

与非门

D触发器

*24.Nios II软核里可以包含以下哪些组件(全部)。 【多选题】

地址发生器

异常控制器、控制寄存器组

程序控制器、通用寄存器组

中断控制器、算数逻辑单元

*25.Cyclone V SoC硬核处理器系统设计中会包含哪些接口或总线(全部)。 【多选题】

AXI-HPS to FPGA

AXI-FPGA to HPS

AXI-Low Height

Avalon-MM

*26.Verilog硬件描述语言中包含的基础类型有(全部) 【多选题】

reg型

wire型

integer型

parameter型

*27.下面关于Avalon-MM总线描述正确的是(ABC) 【多选题】

Avalon-MM是Avalon Memory-Mapped的简写

Avalon-MM总线支持master和slave端进行数据的读写

Avalon-MM主要用于微处理器、存储器、DMA传输等

Avalon-MM不支持master从slave端读取数据

*28.Verilog硬件描述语言中包含的基础类型有(全部)。 【多选题】

reg型

wire型

integer型

parameter型

*29.下列哪些电路属于常用的组合逻辑电路(ABC)。 【多选题】

多路选择器

比较器

38译码器

Pipeline流水线寄存器

*30.关于下面代码说法正确的是(ACD)。

module mult_s (out, clk, a, b);

output [15:0] out;

input clk;

input signed [7:0] a;

input signed [7:0] b;

reg signed [7:0] a_reg;

reg signed [7:0] b_reg;

reg signed [15:0] out;

wire signed [15:0] mult_out;

assign mult_out = a_reg * b_reg;

always @ (posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;

end

endmodule 【多选题】

代码实现的是有符号乘法器

代码实现的是无符号乘法器

乘法器的输入操作数进行了pipeline寄存

乘法器的输出结果进行了pipeline寄存

*31.时钟抖动是指芯片的某一个给定点上时钟周期发生暂时性变化。对

*32.在组合电路中,某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称竞争。对

*33.DFT是指的静态时序分析。错

*34.按位运算或|的优先级高于按位运算与&。错

*35.不可以使用assign语句给variable数据类型赋值。对

*36.wire [n:0] a;表示声明了一个位宽为n的信号。错

*37.`timescale 1ps/1ns表述合法。错

*38.always中可以有assign语句。错

*39.assign语句中的延迟不可综合。对

*40.以下代码实现了一个带异步复位端口的8 位二进制加法器。对

module test(cout,sum,,reset,clk,ina,inb,cin);

input cin;

input [7:0] ina,inb;input rest,clk;

output [7:0] sum;

output cout;

always @(posedge clk or negedge reset)

begin

if(~reset) qout<=0;

end

assign {cout,sum}=ina+inb+cin;

endmodule

*41.FPGA中PLL的英文全称是(Phase Locked loop)。

*42.Timing constraint 指的是(时序约束)

*43.在verilog中,假设a=4’b0010,b=4’b1110,则a && b =(1’b1)。

*44.时钟约束“create_clock -name clk100 -period 10 -waveform {0.00 5.00} [get_ports ClkIn]”

表示约束时钟的占空比为(50)%。

*45.在verilog中,assign c=a>b? a: b中,若a=4’b0010,b=4’b0001,则c=(4’b0010)。

*46.使用verilog硬件描述语言实现一个移位寄存器。

答案:

module shift_reg (clk, shift, sr_in, sr_out);

input clk, shift;

input sr_in;

output sr_out;

reg [66:0] sr;

always @ (posedge clk)

begin

if (shift == 1’b1)

begin

sr[66:1] <= sr[65:0];

sr[0] <= sr_in;

end

end

assign sr_out = sr[65];

endmodule

*47.相对ARM、DSP等处理器,谈谈FPGA具有哪些优势?

功耗低;

可自定义;

管脚多;

延时低;

可实现高度并行化运算;

可实现流水线并行;

*1.下列关于亚稳态描述错误的是()。

电路处于中间状态的时间变长,使得电路“反应”迟钝的现象,叫做亚稳态

对于单比特控制信号采用二级触发器缓冲,可以几乎消除亚稳态

异步FIFO不能用于解决亚稳态问题

对于多比特数据可以采用握手的方式来消除亚稳态

*2.关于FPGA芯片内存储器资源描述错误的是()。

FPGA内部有BLOCK RAM存储器

BLOCK RAM由一定数量固定大小的存储块构成的

使用BLOCK RAM资源需占用额外的逻辑资源,并且速度慢

FPGA内部有由LUT配置成的分布式存储器

*3.关于Quartus软件产生的编程文件描述错误的是()。

FPGA 工程最终生产两种不同用途的文件,它们分别是.sof 和.pof

MCS文件也可用于Quartus编程

sof 是SRAM Object File ,下载到FPGA 中,断电丢失

pof 是Programmer Object File,下载到配置芯片中,上电重新配置FPGA

*4.综合是EDA 设计的关键步骤,下面对综合的描述中错误的是()。

综合就是把抽象设计中的一种表示转换成另一种表示的过程

综合就是将电路的高级语言转换成低级的,可与FPGA/CPLD 相映射的功能网表文件

综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的

为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束

*5.下列标识符中,不合法的标识符是()。

State0

9moon

Not_Ack_0

signall

*6.下列结构不属于Intel FPGA的组成部分的是()。

CLB

PLL

Power CPU

IOB

*7.以下哪个不是Intel FPGA的特点()。

易于使用

实时性好

低延时

支持高级语言(Python等)直接编程

*8.以下电路代表的是()。

译码器

选择器

移位寄存器

锁存器

*9.下列关于任务task和函数function不同点描述错误的是()

函数只能与主模块共用同一个仿真时间单位,而任务可以定义自己的仿真时间单位

函数不能启动任务,而任务能启动其它任务和函数

任务至少要有一个输入变量,而函数可以没有或有多个任何类型的变量

函数返回一个值,而任务则不返回值

*10.下列敏感信号的表示属于边沿敏感型的是()。

always@(posedge clk or posedge clr)

always@(A or B)

always@(posedge clk or clr)

always @ (*)

*11.关于阻塞赋值和非阻塞赋值描述正确的是()。

设计组合逻辑电路时建议使用阻塞赋值

设计时序电路时应尽量使用阻塞赋值方式

可以在两个或者两个以上的always 过程中对同一变量赋值

对同一个变量可以既进行阻塞赋值,又进行非阻塞赋值

*12.已知a=1b’1,b=3b’001,那么{a,b}=()。

‘b0011

(1).A (2).C (3).D (4).D (5).B

(1).C (2).C (3).D (4).A (5).B

(1).D (2).C (3).C (4).D (5).B

*13.已知a=1b’1,b=3b’001,那么{a,b}=()。

‘b0011

‘b001

‘b1001

‘b101

*14.关于锁存器(latch)和触发器(flip-flop)的描述错误的是()。

电平敏感的存储器件称为锁存器

锁存器可分为高电平锁存器和低电平锁存器

触发器是有交叉耦合的门构成的双稳态的存储原件

锁存器为边缘敏感

*15.在FPGA EDA开发工具中,IP的中文含义是()。

网络供应商

知识产权核

系统编程

网络地址

*16.请指出 Altera Cyclone 系列中的 EP1C6Q240C8 这个器件是属于()。

ROM

CPLD

FPGA

GAL

*17.在Quartus工具中,综合和适配步骤的描述正确的是()。

必须先综合才能开始适配

必须先适配才能开始综合

可以不用综合而直接开始适配步骤

综合与适配步骤没有必然联系

*18.Quartus Prime是()公司针对fpga的集成开发工具。

Xilinx

Lattice

Intel

Mentor

*19.下列哪项数据不是在约束文件中定义的()。

管脚属性

FPGA芯片型号

元器件应用领域

以上都是

*20.Quartus 中嵌入式逻辑分析仪是()。

in-system memory content editor

ip catalog

SignalTap

platform designer

*21.给寄存器reg [3:0]cnt赋值十进制数10,下面哪些是正确的()。 【多选题】

cnt <= 10

cnt <= 4’d10

cnt <= 3’d10

cnt <= 4’hA

*22.用于开发、设计、调试包含Intel FPGA 软核处理器的FPGA系统,可能会用到以下哪些工具()。 【多选题】

Qsys

Eclipse

Altera-Modelsim

Quartus

*23.以下哪些是组合逻辑电路中常见的逻辑门()。 【多选题】

与门

与非门

异或门

D触发器

*24.用verilog实现异或逻辑功能,以下正确的是()。 【多选题】

C=A^B

C=A(~B)+(~A)B

C=AB

C=A+B

*25.一个SoC芯片中可以包含以下哪些功能()。 【多选题】

DSP

GPIO

A/D

PLL

*26.以下哪些是SoC FPGA芯片()。 【多选题】

5CSEBA2U19C7

5CSXFC6D6F31C6

EP4CGX30CF19I7

EP4CE10E22C8

*27.下面关于Avalon-ST总线描述正确的是()。 【多选题】

Avalon-ST是Avalon Stream的简写

Avalon-ST主要用于端点间高速、低延迟的数据传输

Avalon-ST总线用于单向传输数据

Avalon-ST总线与Avalon-MM总线接口定义完全一致

*28.在Verilog硬件描述语言中对运算符优先级描述正确的是()。 【多选题】

合并运算符{}优先级最高

条件判断符?:优先级低于逻辑运算符

乘法运算符优先级高于&&逻辑与运算符

算术运算符优先级最低

*29.在Quartus Prime开发环境中可以使用以下哪些方式来进行管脚分配()。 【多选题】

Assignment Editor

Pin Planner

使用Tcl脚本

使用SignalTap

*30.Verilog硬件描述语言中包含的基础类型有()。 【多选题】

reg型

wire型

integer型

parameter型

*31.state,State ,这是两个相同的标识符。

对

错

*32.时序仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

对

错

*33.FPGA的结构是基于SRAM的,掉电后芯片内的信息将不会消失。

对

错

*34.嵌套使用 IF 语句,其综合结果可实现带优先级且条件相与的逻辑电路

对

错

*35.Localparam参数可以在编译时覆盖。

对

错

*36.Verilog对大小写不敏感。

对

错

*37.1234abc可以作为标识符。

对

错

*38.阻塞赋值(=)用于描述组合逻辑,非阻塞赋值(<=)用于描述时序逻辑。

对

错

*39.FPGA内部结构组成部分一般分为三部分:可编程逻辑块( CLB)、可编程I/O 模块和可编程内部连线。

对

错

*40.Tcl是一种脚本语言,它被解释而不是编译。

对

错

*41.SOPC的英文全称为(System-On-Programmable-Chip)。

*42.Intel FPGA嵌入式软核的名称是(Nios/Nios II)。

*43.Intel FPGA 中LAB全称是(Logic Array Block)。

*44.输出不仅取决于当前状态,还和输入有关的状态机称之为(Mealy状态机)。

*45.时钟约束“create_clock -name clk100 -period 10 -waveform {0.00 5.00} [get_ports ClkIn]”

表示约束时钟的周期为(10)ns。

*46.SOPC技术是指什么?SOPC的技术优势是什么?

SOPC技术是以可编程逻辑器件PLD取代ASIC,更加灵活、高效的技术SOC解决方案。

SOPC的技术优势: (1) 运用嵌入的微处理器软核;(2)采用先进的EDA开发工具; (3) 由于连接延迟时间的缩短,SOPC可以提供增强的性能,而且由于封装体积的减小,产品尺寸也减小。

*47.说明FPGA配置有哪些模式,主动配置和从动配置的主要区别是什么?

分为:从动串行模式、从动并行模式、主动串行、主动并行、JTAG模式。主动配置由可编程器件引导配置过程,从动配置则由外部处理器控制配置过程。

*1.电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法不属于面积优化的是()。

资源共享

流水线设计

逻辑优化

串行化

*2.FPGA 的可编程是主要基于什么结构()。

查找表(LUT)

ROM 可编程

PAL 可编程

与或阵列可编程

*3.串行化设计是一种优化方式,下列哪一项对串行化设计描述正确()。

面积优化方法,同时有速度优化效果

速度优化方法,不会有面积优化效果

面积优化方法,不会有速度优化效果

速度优化方法,可能会有面积优化效果

*4.在Quartus工具中,综合和适配步骤的描述正确的是()。

必须先综合才能开始适配

必须先适配才能开始综合

可以不用综合而直接开始适配步骤

综合与适配步骤没有必然联系

*5.下列哪个阶段仿真能仿真出芯片的延迟情况()。

前仿真

功能仿真

时序仿真

以上都不是

*6.在verilog HDL的assign语句建模方法一般称为()方法。

并行赋值

连续赋值

串行赋值

函数赋值

*7.下列关于Moore状态机与Mealy状态机的特征描述错误的是()。

Moore 有限状态机输出只与当前状态有关,与输入信号的当前值无关

从时序上看,Moore状态机属于异步输出状态机

Mealy状态机的输出是现态和所有输入的函数,随输入变化而随时发生变化

Mealy 状态机属于异步输出状态机

*8.时序约束的作用不包括()。

减少逻辑和布线延时

减少资源的消耗

提高设计的工作频率

获得正确的时序分析报告

*9.关于FPGA芯片内存储器资源描述错误的是()。

FPGA内部有BLOCK RAM存储器

BLOCK RAM由一定数量固定大小的存储块构成的

使用BLOCK RAM资源需占用额外的逻辑资源,并且速度慢

FPGA内部有由LUT配置成的分布式存储器

*10.进程中的信号赋值语句,其信号更新是在()。

按顺序完成

在进程最后完成

比变量更快完成

都不对

*11.一个四位十六个状态的格雷码计数器,起始值为1001,经过100个时钟脉冲作用之后的值为()。

0101

0110

0011

0000

*12.在FPGA 设计中对时钟的使用错误的是()。

对时钟进行逻辑操作可增强时钟的稳定性

FPGA 芯片有固定的时钟路由

需要对时钟进行相位移动或变频的时候建议使用FPGA 芯片自带的时钟管理器

FPGA 芯片自带的时钟管理器有减少时钟抖动和偏差的作用

*13.下列关于同步和异步复位描述正确的是()。

同步复位是不受时钟影响

同步复位需要在时钟沿来临的时候才会对整个系统进行复位

使用FPGA设计时芯片的异步复位和同步复位可随意替换使用

同步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控

*14.INTEL FPGA芯片不包括()。

Cyclone V

Kintex-7

Arria

Stratix

*15.以下不属于硬件描述语言的是()。

VHDL

Verilog

JAVA

AHDL

*16.关于Quartus软件产生的编程文件描述错误的是()。

FPGA 工程最终生产两种不同用途的文件,它们分别是.sof 和.pof

MCS文件也可用于Quartus编程

sof 是SRAM Object File ,下载到FPGA 中,断电丢失

pof 是Programmer Object File,下载到配置芯片中,上电重新配置FPGA

*17.下列关于Verilog语言数字表示错误的是()。

2’b01

16’d123a

10’h17b

8’h55

*18.以下程序执行后,变量a的值为()。

wire[7:0] a;

wire[3:0] b;

wire[3:0] c;

assign b =4’h5;

assign c =4’ha;

assign a = b + c;

8’ha5

8’hf

8’h5

8’h5a

*19.已知reg的setup,hold时间,时钟周期为period,则中间组合逻辑的delay范围为()。

Delay < period - setup – hold

Delay > period - setup – hold

Delay > period + setup + hold

Delay < period - setup + hold

*20.以下代码描述的是()。

module test(Q,D,CLK)

input D,CLK;

output Q;

reg Q;

always @ (posedge CLK)

begin Q <= D; end

endmodule

基本D触发器

锁存器

加法器

乘法器

*21.Cyclone V SoC FPGA里有以下哪些资源()。 【多选题】

HPS(Hard Process System)

LAB

时钟资源

IOB

*22.FPGA中LAB会有以下哪些资源()。 【多选题】

LE

ALM

DSP

LUT

*23.用于开发、设计、调试包含Intel FPGA 软核处理器的FPGA系统,可能会用到以下哪些工具()。 【多选题】

Eclipse

Altera-Modelsim

Qsys

Quartus

*24.以下哪些FPGA芯片是可以使用Nios 软核处理器的()。 【多选题】

5CSEBA2U19C7

5CSXFC6D6F31C6

EP4CGX30CF19I7

EP4CE10E22C8

*25.通过下面哪些手段,FPGA可以降低深度学习的延时()。 【多选题】

充分利用整个芯片的并行性,降低计算延迟

拥有更多的计算单元和DDR3内存

拥有灵活可定制的IO,实现了确定的低IO延迟

紧密耦合的高带宽内存,并且支持可编程数据路径

*26.对FPGA流水线结构描述正确的有()。 【多选题】

流水线设计实际上就是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组暂存中间数据

流水线设计是牺牲面积换速度的一种方法,可以大大提高电路的工作频率

FPGA支持的流水线级数与CPU一样,是官方公布的,不能通过硬件或软件进行更改

FPGA流水线设计可以用来做实时处理,这也是FPGA广泛应用于通讯与视频领域的一个原因

*27.对FPGA中查找表(LUT)描述正确的有()。 【多选题】

查找表(LUT)本质上是一个RAM,在FPGA中用来进行逻辑运算的单元

LUT具有和逻辑电路相同的功能,且具有更快的执行速度,并能完成更大规模的运算

查找表(LUT)资源可以用来实现寄存器的功能

FPGA使用LUT结构,CPLD中没有LUT

*28.一个SoC芯片中可以包含以下哪些功能()。 【多选题】

DSP

GPIO

A/D

PLL

*29.在Verilog中,下列哪些语句属于分支语句()。 【多选题】

if-else

Switch

Case

While

*30.对FPGA器件的接口描述正确的有()。 【多选题】

FPGA具有大量可自定义的输入输出接口

FPGA中某些硬核IP资源的管脚被限定到了一些管脚上

FPGA的IO口,主要是按数字逻辑信号(高电平与低电平)的方式的输出

FPGA具有大量的IO口,因此FPGA适合并口通讯,不适合串行口通讯

*31.Verilog关键字里面只有小写字母。

对

错

*32.Tcl支持控制代码执行流程的通用控制结构,包括条件命令和循环。支持的条件命令包括if then else命令和switch语句。

对

错

*33.通过Quartus软件中的Pin Planner可以对Intel FPGA器件的管脚输出驱动电流进行修改。

对

错

*34.功能仿真与时序仿真的结果是完全一致的。

对

错

*35.DSP buider不仅支持将Simulink 模型转换为VHDL/Verilog 代码,也支持将matlab程序转换为 VHDL/Verilog 代码?

对

错

*36.时钟抖动是指芯片的某一个给定点上时钟周期发生暂时性变化。

对

错

*37.在组合电路中,某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称竞争。

对

错

*38.异步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

对

错

*39.if-else语句与case语句都具有优先级。

对

错

*40.1234abc可以作为标识符。

对

错

*41.Intel FPGA嵌入式软核的名称是(Nios/Nios II)。

*42.HLS的英文全称是(High-Level Synthesis)。

*43.FPGA的优化过程主要是速度与(资源或面积)的优化过程。

*44.在Quartus中,将硬件描述语言转换为一些由与、或、非,触发器,RAM等基本逻辑单元组成的逻辑网表这个过程是(综合)。

*45.在Verilog编程中,有一个变量类型,相对与电路的导线可以将两个或多个信号连接到一起,这个变量类型是(wire类型)。

*46.结合您的理解,简述Verilog语句中阻塞赋值与非阻塞赋值的含义与区别,已经各自的适用的场景。

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“<=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。

Verilog语言中讲的阻塞赋值与非阻塞赋值,但从字面意思来看,阻塞就是执行的时候在某个地方卡住了,等这个操作执行完在继续执行下面的语句,而非阻塞就是不管执行完没有,我不管执行的结果是什么,反正我继续下面的事情。而Verilog中的阻塞赋值与非阻塞赋值正好也是这个意思。

阻塞语句的使用:

(1)在时序逻辑电路中一般使用非阻塞赋值。

非阻塞赋值在块结束后才完成赋值操作,此赋值方式可以避免在仿真出现冒险和竞争现象。

(2)在组合逻辑电路中一般使用阻塞赋值。

使用阻塞方式对一个变量进行赋值时,此变量的值在在赋值语句执行完后就立即改变。

(3)在assign语句中必须使用阻塞赋值语句。

*47.相对ARM、DSP等处理器,谈谈FPGA具有哪些优势?

功耗低;

可自定义;

管脚多;

延时低;

可实现高度并行化运算;

可实现流水线并行;

*1.下列关于亚稳态描述错误的是()。

电路处于中间状态的时间变长,使得电路“反应”迟钝的现象,叫做亚稳态

对于单比特控制信号采用二级触发器缓冲,可以几乎消除亚稳态

对于多比特数据可以采用握手的方式来消除亚稳态

异步FIFO不能用于解决亚稳态问题

*2.下列优化方法中哪两种是提高运行速度(速度优化)方法:()。

①流水线设计 ②资源共享 ③逻辑优化 ④串行化 ⑤寄存器配平 ⑥关键路径法

①⑤

②③

②⑥

①⑥

*3.在FPGA 设计中对时钟的使用错误的是()。

对时钟进行逻辑操作可增强时钟的稳定性

FPGA 芯片有固定的时钟路由

需要对时钟进行相位移动或变频的时候建议使用FPGA 芯片自带的时钟管理器

FPGA 芯片自带的时钟管理器有减少时钟抖动和偏差的作用

*4.基于EDA软件的FPGA / CPLD 设计流程为:()。

原理图/HDL 文本输入→功能仿真→ 综合→ 适配→ 时序仿真→ 编程下载→测试。

原理图/HDL 文本输入→时序仿真→ 综合→ 适配→ 功能仿真→ 编程下载→测试。

原理图/HDL 文本输入→功能仿真→ 适配→ 综合→ 时序仿真→ 编程下载→测试。

原理图/HDL 文本输入→功能仿真→ 时序仿真→ 综合→ 适配→ 编程下载→测试。

*5.大规模可编程器件主要有CPLD 和FPGA 两类,下面对FPGA 结构与工作原理描述中,正确的是()。

FPGA 全称为复杂可编程逻辑器件

FPGA 是基于哈佛结构的可编程逻辑器件

基于SRAM 的FPGA 器件,每次上电后必须进行一次配置

在Intel公司生产的器件中, MAX7000 系列属于FPGA结构

*6.已知reg的setup,hold时间,时钟周期为period,则中间组合逻辑的delay范围为()。

Delay < period - setup – hold

Delay > period - setup – hold

Delay > period + setup + hold

Delay < period - setup + hold

*7.下列EDA软件中,哪一个不具有逻辑综合功能()。

Max+Plus II

ModelSim

Quartus II

Synplify

*8.在处理常数乘法的时候,若还是使用乘法器将会造成大量的不必要的面积开销,可以使用移位加法代替,若要实现b*10,则下列最优选项为()。

b*10

(b+b+b+b+b) << 1

b<<3+b<<1

b<<4-b<<2-b<<1

*9.Intel Cyclone器件不支持的配置方式()。

JTAG 模式

PS 模式

32位并行配置

AS 模式

*10.针对Verilog HDL 语言中的case语句说法不正确的是()。

case 语句表达式的取值可以超出语句下面列出的值的范围

语句各分支表达式允许同时满足case表达式的值

条件语句中的选择值需要完整覆盖表达式的取值范围

保险起见,case语句最后分枝最好都加上default 语句

*11.关于阻塞赋值和非阻塞赋值描述正确的是()。

设计时序电路时应尽量使用阻塞赋值方式

设计组合逻辑电路时建议使用阻塞赋值

可以在两个或者两个以上的always 过程中对同一变量赋值

对同一个变量可以既进行阻塞赋值,又进行非阻塞赋值

*12.实现下列结果正确表达式为()。

assign out=sel? in1:in0

assign out=sel&& in1&&in0

assign out=sel||in1||in0

assign out=sel|| in1&&in0

*13.目前FPGA设计输入,即设计方法有多种,以下哪个不是开发FPGA的方法()。

原理图式设计方法

VHDL语言描述设计方法

Verilog 语言描述设计方法

在非嵌入式开发中,利用纯C 语言设计描述

*14.以下代码描述的是()。

module test(Q,D,CLK)

input D,CLK;

output Q;

reg Q;

always @ (posedge CLK)

begin Q <= D; end

endmodule

基本D触发器

锁存器

加法器

乘法器

*15.a=5’b11001;b=3’b101;则c=a&b的结果为()。

3’b001

5’b00001

5’b11001

5’b11111

*16.下列异或操作结果错误的是()。

0 XOR 1 = 0

0 XOR 0 = 0

1 XOR 1 = 0

1 XOR 0 =1

*17.INTEL FPGA芯片不包括()。

Cyclone V

Kintex-7

Arria

Stratix

*18.大规模可编程器件主要有CPLD 和FPGA 两类,其中CPLD 通过()实现其逻辑功能。

查找表(LUT)

输入缓冲

可编程乘积项逻辑

输出缓冲

*19.如果网线型变量说明后未使用,那么其缺省值为(Z)

0

1

z

x

*20.以下代码描述的是()。

module test(Q,D,CLK)

input D,CLK;

output Q;

reg Q;

always @ (posedge CLK)

begin Q <= D; end

endmodule

基本D触发器

锁存器

加法器

乘法器

*21.Intel FPGA都有以下哪几个系列()。 【多选题】

Cyclone

Stratix

Arria

AgileX

*22.Cyclone V SoC FPGA里有以下哪些资源()。 【多选题】

HPS(Hard Process System)

LAB

时钟资源

IOB

*23.Intel FPGA中Nios II可以挂载以下哪些IP核()。 【多选题】

PIO

UART

DMA

SDRAM控制器

*24.用于开发、设计、调试包含Intel FPGA 软核处理器的FPGA系统,可能会用到以下哪些工具()。 【多选题】

Qsys

Eclipse

Altera-Modelsim

Quartus

*25.以下属于常见的Avalon总线接口的是哪些()。 【多选题】

Avalon-MM

Avalon-ST

Avalon-XX

AXI

*26.以下哪些是SoC FPGA芯片()。 【多选题】

5CSEBA2U19C7

5CSXFC6D6F31C6

EP4CGX30CF19I7

EP4CE10E22C8

*27.以下哪些FPGA芯片是可以使用Nios 软核处理器的()。 【多选题】

5CSEBA2U19C7

5CSXFC6D6F31C6

EP4CGX30CF19I7

EP4CE10E22C8

*28.Cyclone V SoC硬核处理器系统设计中会包含哪些接口或总线()。 【多选题】

AXI-FPGA to HPS

AXI-HPS to FPGA

AXI-Low Height

Avalon-MM

*29.以下哪些语言可以用于FPGA设计()。 【多选题】

VHDL

Verilog

Java

C#

*30.以下表示十进制数值155,正确的是()。 【多选题】

16’d155

16’h9B

16’o233

16’b10011011

*31.FPGA的全称是Field-Programmable Gate Array。

对

错

*32.FPGA 的基本可编程逻辑单元是由查找表和寄存器组成的,查找表完成纯组合逻辑功能。

对

错

*33.wire [n:0] a;表示声明了一个位宽为n的信号。

对

错

*34.{a,{2{c,d}}}等同于{a,c,c,d,d}。

对

错

*35.以下代码实现了一个3-8译码器。

module test(clk,reset,en,in,out);

iput clk,reset,en,in;output[3:0] out;reg[3:0] out;

always @(posedge clk)

begin if(reset) out<=4 ’h0;

else if(en) out<={out,in};

end

endmodule

对

错

*36.FPGA内部结构组成部分一般分为三部分:可编程逻辑块( CLB)、可编程I/O 模块和可编程内部连线。

对

错

*37.功能仿真与时序仿真的结果是完全一致的。

对

错

*38.使用Intel FPGA进行设计时应避免使用全局时钟网络,从而保证更好的时钟性能。

对

错

*39.if-else语句与case语句都具有优先级。

对

错

*40.1234abc可以作为标识符。

对

错

*41.SOC系统又称为(芯片级系统)系统。SOPC系统又称为(可编程片上系统)系统。

*42.FPGA中的LUT一般都是用来实现(组合)逻辑功能。

*43.如果ain=3’b011,bin=3’b110,则{ain,bin}为(6’b011110)。

*44.assign ain = (bin > 4’d3) ? 1:0; 如果bin的值为6,则ain上的值为(1)。

*45.竞争与冒险通常出现在(组合)逻辑电路中。

*46.SOC技术含义是什么?什么是SOPC?

SOC就是将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)、数据通路、与外部系统的数据接口等部件集成在单一芯片上。

SOPC就是基于可编程逻辑器件的SOC设计方案

*47.FPGA是基于什么结构的可编程逻辑器件?其基本结构由哪几部分组成?

FPGA是基于SRAM查找表的可编程结构。FPGA的核心部分是逻辑单元阵列LCA,LCA是由内部逻辑块矩阵和周围I/O接口模块组成。LCA内部连线在逻辑块的行列之间,占据逻辑块I/O接口模块之间的通道,可以由可编程开关以任意方式连接形成逻辑单元之间的互连。