当前位置:首页

> 2022年8月

按键消抖

按键消抖主要针对的是机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,—个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。 ...

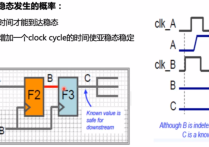

CDC跨时钟域信号处理

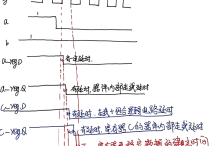

保证时序电路的时序要求:建立时间:在有效的时钟沿到来之前,输入端的输入信号需要保持稳定不变的最小时间保持时间:在有效的时钟沿到来之后,输入端的输入信号需要保持稳定不变的最小时间...

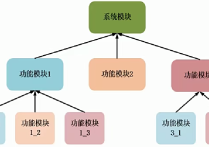

时序约束(TCL脚本)

get_ports的使用方法如下:# 获取所有端口 get_ports * # 获取名称中包含data的端口 get_ports *data* # 获取所有输出端口 get_ports -filter {DIRECTION == OUT} # 获取所有输入端口 all...

FPGA时序分析和时序约束

时序分析:时序分析的目的就是通过分析FPGA设计中各个寄存器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟之间的关系。一个设计OK的系统,必然能够保证整个系统中所有的寄存器都能够正确的寄存数据。数据和时钟传输路径是由EDA软件,通过针对特定器件布局布线得到的。时序约束:两个作用告知 EDA 软件...