“EBAZ4205原理图和PCB免费分享 基于ZYNQ7010” 的相关文章

ALGO C4MB V11引脚参照表(持续更新)

功能:常用引脚CLKPIN_E1LED0PIN_G15LED1PIN_F16LED2PIN_F15LED3PIN_D16KEY1PIN_E15KEY2PIN_E16KEY3PIN_M15KEY4PIN_M16RXDPIN_M2TXDPIN_G1功能:VGA引脚VGA_BLUE[0]PIN_C15VG...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...

3-8译码器

译码:译码是编码的逆过程,在编码时,每一种二进制的代码,都赋予了特殊的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。译码器:一类多输入多输出的组合逻辑电路器件,其可以分为:变量译码和显示译码两类3-8译码器 模块框图:输出信号定义为...

全加器(层次化设计)

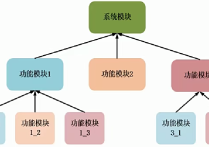

该篇博客根据上一篇半加器的设计,再结合层次化的设计思想来实现一个全加器!层次化设计理论部分:数字电路中根据模块层次的不同有两种基本的结构设计方法:自底向上的设计方法 和 自顶向下的设计方法自底向上(Bottom-Up) 自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存...