# **Intel® Acceleration Stack User Guide**

# **Intel FPGA Programmable Acceleration Card** N3000

Updated for Intel® Acceleration Stack for Intel® Xeon® CPU with FPGAs: 1.1

Version: **2021.06.14**

ID: 683040

# **Contents**

| 1. About this Document                                                                |    |

|---------------------------------------------------------------------------------------|----|

| 1.1. Acronym List                                                                     | 5  |

| 2. System Requirements                                                                |    |

| 2.1. Cooling Requirements                                                             | 7  |

| 3. Hardware Installation                                                              | 11 |

| 3.1. Installing the Intel FPGA PAC N3000                                              | 11 |

| 4. Installing the OPAE Software                                                       | 16 |

| 4.1. Install Additional Packages                                                      |    |

| 4.2. Install the Release Package                                                      |    |

| 4.2.1. Remove Previous OPAE Packages4.2.2. Install the Acceleration Stack for Runtime |    |

| 4.2.3. Install the Acceleration Stack for Development                                 |    |

| 4.2.4. Verify the OPAE Installation                                                   |    |

| 4.2.5. Install the Configuration Files                                                |    |

| 4.3. Identify the Intel MAX 10 Version on your Intel FPGA PAC N3000                   |    |

| 4.3.1. FPGA Factory Image Overview                                                    | 24 |

| 5. OPAE Tools                                                                         |    |

| 5.1. Using fpgasupdate                                                                |    |

| 5.2. Using fpgainfo                                                                   |    |

| 5.3. Test PCIe and External Memories with fpgabist                                    |    |

| 6. Sample Test: Native Loopback                                                       |    |

|                                                                                       |    |

| 7. Installing the Intel XL710 Driver                                                  |    |

| 7.1. Updating the Intel XL710 Firmware                                                | 34 |

| 8. Configuring Ethernet Interfaces                                                    | 38 |

| 8.1. Modifying the Interface Maximum Transmission Unit (MTU) Size                     |    |

| 8.2. Setting Forward Error Correction (FEC) Mode                                      |    |

| 8.3. Ethernet Pause Flow Control                                                      |    |

|                                                                                       |    |

| 9. Testing Network Loopback Using Data Plane Development Kit (DPDK)                   |    |

| 9.1. Test Using an External Traffic Generator                                         |    |

| 9.3. Troubleshooting in DPDK                                                          |    |

| 9.4. Revert Back from DPDK to OPAE                                                    |    |

| 10. Graceful Shutdown                                                                 | 57 |

| 10.1. Background                                                                      |    |

| 10.2. Using OPAE                                                                      |    |

| 10.3. Using DPDK                                                                      | 60 |

| 11. Single Event Upset (SEU)                                                          | 61 |

| 11 1 OPAE Handling of SELL                                                            | 61 |

| 11.2. DPDK Handling of SEU                                                                   | 63 |

|----------------------------------------------------------------------------------------------|----|

| 12. Document Revision History for Intel Acceleration Stack User Guide: Intel FPGA PAC N3000  |    |

| A. Troubleshooting                                                                           | 66 |

| A.1. If OPAE installation verification fails, how to install OPAE manually?                  | 66 |

| B. Upgrade your Intel FPGA PAC N3000 with Production Version of BMC and Intel Arria 10 Image | 67 |

| B.1. Upgrading from 1.1 Beta to Production Version                                           |    |

| B.1.1. Root Entry Hash Programmed                                                            |    |

| B.2. Upgrading from 1.1 Alpha-2 or Older to Production Version                               | 70 |

| C. Configure the 4.19 Kernel                                                                 | 76 |

| D. fpgabist Sample Output                                                                    | 77 |

| D.1. For 2x2x25G Configuration                                                               | 77 |

| D 2 For 8x10G Configuration                                                                  | 85 |

# 1. About this Document

This document provides:

- Instructions and requirements for installing the Intel FPGA Programmable Acceleration Card N3000 into a server.

- Instructions for installing the Open Programmable Acceleration Engine (OPAE) software on host Intel<sup>®</sup> Xeon<sup>®</sup> processor for managing and accessing the Intel FPGA PAC N3000.

- Instructions for installing the OPAE tools for validation of the Intel FPGA PAC N3000.

- Instructions for running built-in self-tests using the FPGA factory image.

- Instructions for installing the Intel XL710 driver and network testing tools for testing the ethernet capabilities.

- Information about Graceful Shutdown and Single Event Upset (SEU) handling.

The Intel Acceleration Stack for Intel Xeon CPU with FPGAs is a collection of software, firmware, and tools that allows both software and RTL developers to take advantage of the power of Intel FPGA PAC N3000. By offloading computationally intensive networking tasks to the FPGA, the acceleration platform allows the Intel Xeon processor to execute other critical processing tasks.

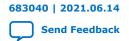

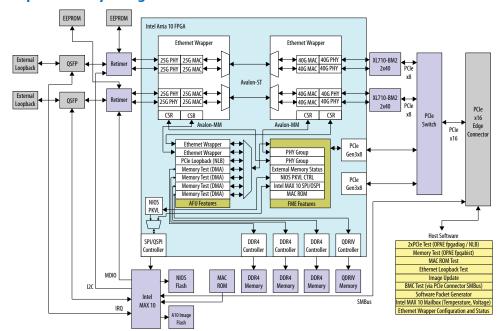

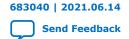

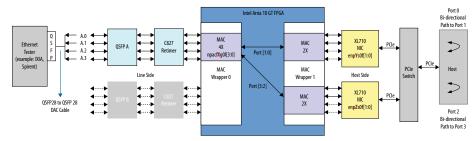

Figure 1. Block Diagram

# 1.1. Acronym List

| Acronym        | Expansion                                    | Description                                                                                                                                        |

|----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel FPGA PAC | Intel FPGA Programmable<br>Acceleration Card | Intel FPGA PAC N3000 is a full-duplex 100 Gbps in-system re-programmable acceleration card for multi-workload networking application acceleration. |

| AFU            | Accelerator Functional<br>Unit               | Hardware Accelerator implemented in FPGA logic which offloads a computational operation for an application from the CPU to improve performance.    |

| AF             | Acceleration Function                        | Compiled Hardware Accelerator image implemented in FPGA logic that accelerates an application.                                                     |

| API            | Application Programming<br>Interface         | A set of subroutine definitions, protocols, and tools for building software applications.                                                          |

| FIU            | FPGA Interface Unit                          | FIU is a platform interface layer that acts as a bridge between platform interfaces like PCIe* and AFU-side interfaces such as CCI-P.              |

| OPAE           | Open Programmable<br>Acceleration Engine     | The OPAE is a set of drivers, utilities, and API's for managing and accessing AFs.                                                                 |

|                |                                              | continued                                                                                                                                          |

| Acronym | Expansion              | Description                                                                                                                                                                                                                                 |

|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FME     | FPGA Management Engine | The FME provides information about the FPGA platform including the OPAE version.                                                                                                                                                            |

| OTSU    | One-Time Secure Update | Updates the Intel MAX® 10 Board Management Controller (BMC) with new image files to enable the Root of Trust (RoT) features.                                                                                                                |

| RSU     | Remote System Update   | An RSU operation sends an instruction to the device to trigger a power cycle of the Intel FPGA PAC N3000 only. This will force reconfiguration from flash for either Intel MAX 10 BMC image (on devices that support it) or the FPGA image. |

# 2. System Requirements

- Operation System:

- CentOS Linux version 7.6 kernel 3.10 or kernel 4.19<sup>(1)</sup>

- Red Hat\* Enterprise Linux\* (RHEL) version 7.6 kernel 3.10

For information about the latest OS support, refer to the Getting Started page.

- Connectivity hardware for testing the Ethernet interfaces:

- 10 Gbps QSFP+

- 25 Gbps QSFP28

Refer to the Intel FPGA Programmable Acceleration Card N3000 Data Sheet for the following:

- List of supported QSFP+ and QSFP28 modules.

- Information on Intel FPGA PAC N3000 ordering part numbers (OPNs) that support Intel Acceleration Stack 1.1 production version.

While selecting a server, ensure that the server meets the following requirements (per slot):

- Power

- Cooling air flow

- Physical dimension

For more information, refer to the Intel FPGA Programmable Acceleration Card N3000 Data Sheet.

Note:

To compile an AFU using the Intel Quartus® Prime Pro Edition software, your server must have at least 48 GB of system RAM.

# 2.1. Cooling Requirements

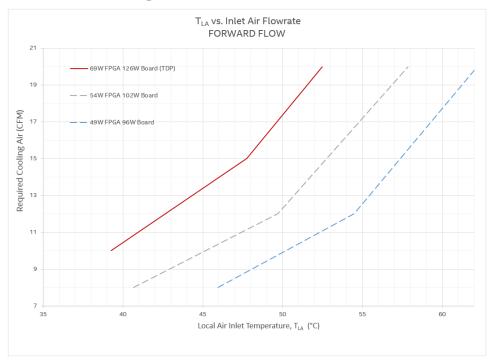

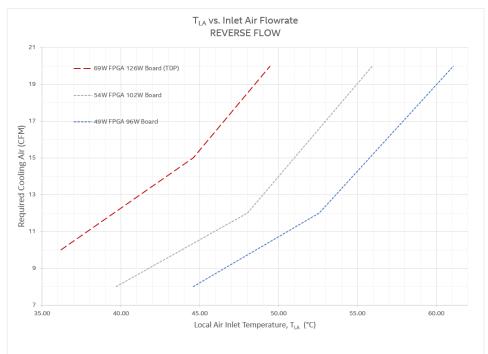

The high performance devices installed on the Intel FPGA PAC N3000 require server based forced air cooling to maintain proper operating temperature. This section provides air flow requirements for the Intel FPGA PAC N3000. Sufficient airflow keeps the Intel Arria<sup>®</sup> 10 GT junction temperature below 95 °C. Each data point corresponds to minimum airflow (Y-axis) through the card for a corresponding card inlet temperature (X-axis).

<sup>(1)</sup> Refer to Configure the 4.19 Kernel on page 76 to support OPAE installation.

Figure 2. Air Flow Pattern

#### Key parameters:

- Required Cooling Airflow (CFM): Volumetric flow rate, in cubic feet per minute, of air passing through the PCIe faceplate of the Intel FPGA PAC N3000.

- T<sub>1</sub> FPGA Junction Temperature

- T<sub>LA</sub> Local Ambient Temperature<sup>(2)</sup>: Temperature of forced air as it enters the Intel FPGA PAC N3000.

Note: In many systems,  $T_{LA}$  is higher than the room ambient due to heating affects of chassis components.

<sup>(2)</sup> T<sub>LA</sub> values shown in the tables and charts of this section are informational, and may represent conditions outside of the supported operating range.

#### **Table 1.** Power and Thermal Requirements

The Intel FPGA PAC N3000 uses a passive heatsink. The server must provide sufficient forced airflow to keep the FPGA within the following operating conditions:

| Parameters                                                    | Maximum Values |

|---------------------------------------------------------------|----------------|

| Intel Arria 10 FPGA Thermal Design Power (TDP) <sup>(3)</sup> | ≤ 69 W         |

| Intel FPGA PAC N3000 Thermal Design Power (TDP)               | ≤ 126 W        |

| Recommended FPGA Maximum Operating Temperature                | 95°C           |

| FPGA T <sub>J-MAX</sub> or Thermal Protection Shutdown        | 100°C          |

| Maximum T <sub>LA</sub> (forward airflow)                     | 51°C           |

| Maximum T <sub>LA</sub> (reverse airflow)                     | 45°C           |

Figure 3. Forward Flow Cooling Curve

<sup>(3)</sup> Intel Arria 10 FPGA TDP cannot be obtained from on-board BMC sensors. Use the Intel Quartus Prime Power Analyzer to verify compliance with this value for your design.

Table 2. Local Air Inlet Temperature and Air Flow Values for Forward Cooling

| To maintain T <sub>J</sub> = 95°C |                |                                          |    |                                                |                |  |

|-----------------------------------|----------------|------------------------------------------|----|------------------------------------------------|----------------|--|

| FPGA Pow<br>Board Pow             |                | FPGA Power < 54 W<br>Board Power < 102 W |    | FPGA Power < 69 W<br>Board Power < 126 W (TDP) |                |  |

| Max. T <sub>LA</sub> (°C)         | Air Flow (CFM) | Max. T <sub>LA</sub> (°C) Air Flow (CFM) |    | Max. T <sub>LA</sub> (°C)                      | Air Flow (CFM) |  |

| 46                                | 8              | 40.7                                     | 8  | 39.2                                           | 10             |  |

| 54.5                              | 12             | 49.8                                     | 12 | 47.8                                           | 15             |  |

| 62                                | 20             | 57.9                                     | 20 | 52.3                                           | 20             |  |

Figure 4. Reverse Flow Cooling Curve

Table 3. Local Air Inlet Temperature and Air Flow Values for Reverse Cooling

| To maintain T <sub>J</sub> = 95°C |                          |                                         |                          |                                                |                |  |

|-----------------------------------|--------------------------|-----------------------------------------|--------------------------|------------------------------------------------|----------------|--|

| FPGA Pow<br>Board Pow             | rer < 49 W<br>ver < 96 W |                                         | rer < 54 W<br>er < 102 W | FPGA Power < 69 W<br>Board Power < 126 W (TDP) |                |  |

| Max. T <sub>LA</sub> (°C)         | Air Flow (CFM)           | Max. T <sub>LA</sub> (°C) Air Flow (CFM |                          | Max. T <sub>LA</sub> (°C)                      | Air Flow (CFM) |  |

| 44.6                              | 8                        | 39.8                                    | 8                        | 36.1                                           | 10             |  |

| 52.6                              | 12                       | 48                                      | 12                       | 44.7                                           | 15             |  |

| 61                                | 20                       | 56                                      | 20                       | 49.4                                           | 20             |  |

Note:

These flow curves are based on numerical analysis and should be used as a starting point for thermal design estimation. Thermal performance of host systems may vary. Therefore, you should perform in-system thermal validation.

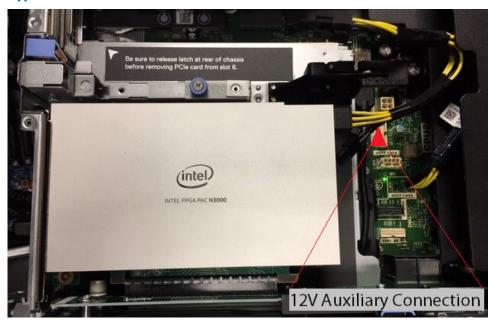

# 3. Hardware Installation

To operate the Intel FPGA PAC N3000 in your server, you must have the following:

- PCI Express\* Gen3x16 slot with physical space for a full height half length PCIe form factor board

- Auxiliary 12 V 6-pin power connector

- Server that provides sufficient airflow for a given air inlet temperature

Note: The Intel FPGA PAC N3000 cannot operate without the 6-pin auxiliary power

connector. Internal board circuitry prevents operation without the auxiliary power

source and PCIe connector power source.

Note: If the Intel FPGA PAC N3000 is not integrated into a server closed loop fan control system, you must set the fan speed to 100%. The fan speed (100%) setting must be applied to avoid overheating when the server turns on. When the BMC detects that the

card has overheated, it powers down the card to prevent damage.

#### Figure 5. Typical Intel FPGA PAC N3000 Installation in a Server

# 3.1. Installing the Intel FPGA PAC N3000

Complete these steps to install the Intel FPGA PAC N3000:

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

- 1. Power down the system.

- 2. Plug the Intel FPGA PAC N3000 into a PCIe x16 physical and x16 electrical slot on the motherboard.

- Connect the auxiliary power to the 12 V 6-pin connector using an applicable cable.

Note: Make sure the auxiliary power cable does not block airflow to the Intel FPGA PAC N3000.

- 4. Enable the following options in the BIOS:

- Intel VT-x (Intel Virtualization Technology for IA-32 and Intel 64 Processors)

- Intel VT-d (Intel Virtualization Technology for Directed I/O)

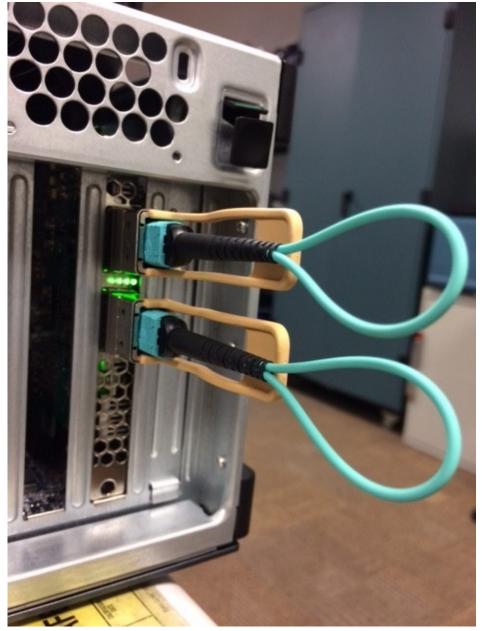

- 5. For network testing, you can insert a loopback module into each QSFP28 port.

Note: ESD protection is required while handling the Intel FPGA PAC N3000.

**Warning:** Take caution when you are inserting and removing the cards into PCIe slots. The bottom side of the card has capacitors and resistors that can be knocked off if the cards scrapes against edges or corners of the slot in the chassis.

#### Figure 6. Example of QSFP Non-optical Modules

This is a 25 GbE QSFP setup.

#### Figure 7. Example of QSFP Loopback Optical Modules

This figure shows the correct orientation of the QSFP module for optical loopback testing. The loopback configuration consists of two Intel 40GBASE-SR4 QSFP+ optical modules and two 10Gtek 12-Core MPO OM3 Fiber Optic Loopback Cables.

6. Power on the system and observe the Ethernet status LEDs which are located between the QSFP connectors. The LED operation is described in the table below:

Table 4. LED Behavior

| LED Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                          | Yellow means link is up with link speed of 10G.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Connectivity LED         | Green means link is up with link speed of 25G.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                          | Off means link is down.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| A skin that I ED         | Green blinking at 1 Hz means link activity present.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Activity LED             | Off means link is down or no activity.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| All LEDs blinking yellow | It means either:  12 V Auxiliary or PCIe edge supply voltage is below 10.46 V or FPGA core temperature reaches 100°C or Board temperature reaches 85°C You should check the following: Card insertion in PCIe slot. 12 V Auxiliary connection on the Intel FPGA PAC N3000 and on the server motherboard. Fan setting for cooling air flow. Sufficient airflow is required whenever the Intel FPGA PAC N3000 is powered on. |  |  |  |

For details on the location of Connectivity and Activity LEDs, refer to the Intel FPGA Programmable Acceleration Card N3000 Data Sheet.

#### Figure 8. Ethernet Status LEDs Power-On Indication

This figure is an example of 25G configuration where both Ethernet links are UP with ongoing Ethernet activity.

#### 3. Hardware Installation

683040 | 2021.06.14

Note:

If your server is set up with secure boot, the OPAE Remote Setup (RSU) command will not function. This RSU limitation is due to secure boot having the following limitations:

- Using kexec to start an unsigned kernel image.

- Hibernation and resume from hibernation.

- User-space access to physical memory and I/O ports.

- Module parameters that allow setting memory and I/O port addresses.

- Writing to MSRs through /dev/cpu/\*/msr.

- Use of custom ACPI methods and tables.

- ACPI APEI error injection.

While you implement secure boot in your server, you must power cycle your server to load a new FPGA image rather than using the RSU command.

# 4. Installing the OPAE Software

The OPAE is a software framework delivered as part of the Intel Acceleration Stack for managing and accessing the Intel FPGA PAC.

The following section describes the installation of OPAE on a freshly imaged server with supported OS and kernel. The host must have internet connectivity to retrieve additional software packages. The installation steps require sudo or root privileges on your host.

Note:

The OPAE version created for Intel FPGA PAC N3000 is not compatible with any other Intel FPGA PAC.

To verify that you have the correct kernel, kernel source and header, perform the following steps:

1. Check the kernel version running on the server:

```

$ uname -a

```

#### Sample output:

```

Linux rae-xxx 3.10.0-957.el7.x86_64

```

2. List the kernel source on the system:

```

$ ls -l /usr/src/kernels/

```

#### Sample output:

```

drwxr-xr-x. 22 root root 4096 Jun 21 13:05 3.10.0-957.el7.x86_64

```

3. List the installed kernel header:

```

$ rpm -qa | grep kernel-header

kernel-headers-3.10.0-957.el7.x86_64

```

If the kernel source and header do not match the kernel version running on the server, there can be issues with installing OPAE driver.

To mitigate this issue:

1. Remove the incompatible kernel header:

```

$ sudo yum remove kernel-headers.x86_64

```

2. Install the correct kernel source:

```

$ sudo yum install "kernel-devel-uname-r == $(uname -r)"

```

3. Install the correct kernel header:

```

$ sudo yum install kernel-headers-`uname -r`

```

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

## 4.1. Install Additional Packages

Before you install and build the OPAE software, you must install the required packages. Run the following commands:

```

$ sudo yum install gcc gcc-c++ \

cmake make autoconf automake libxml2 \

libxml2-devel json-c-devel boost ncurses ncurses-devel \

ncurses-libs boost-devel libuuid libuuid-devel python2-jsonschema \

doxygen hwloc-devel libpng12 rsync openssl-devel \

bc python-devel python-libs python-sphinx openssl python2-pip

$ sudo pip install intelhex

```

For Red Hat Enterprise Linux (EPEL) system, run the following commands to install the addtional packages:

```

$ sudo subscription-manager repos --enable "rhel-*-optional-rpms" \

--enable "rhel-*-extras-rpms" --enable "rhel-ha-for-rhel-*-server-rpms"

$ sudo yum install https://dl.fedoraproject.org/pub/epel/epel-release-\

latest-7.noarch.rpm

```

For CentOS system, run the following command to install the extra repository:

```

$ sudo yum install epel-release

```

# 4.2. Install the Release Package

Before installing the release package, ensure that the Intel FPGA PAC N3000 is installed properly as mentioned in the Hardware Installation on page 11.

The installers for Intel FPGA PAC N3000 allow easy installation of the release package.

Acceleration Stack Installers

To install the Acceleration Stack, select either the **Acceleration Stack for Runtime** (n3000\_ias\_1\_1\_pv\_rte\_installer.tar.gz) or the **Acceleration Stack for Development** (n3000\_ias\_1\_1\_pv\_dev\_installer.tar.gz). Each package includes three components:

- 1. Runtime (rte) or Development (dev) Acceleration Stack installer script (n3000-1.3.6-\*-setup.sh)

- Firmware files (N3000\_XL710\_firmware.zip) To update the Intel XL710 Firmware.

- 3. Supplemental files (N3000\_supplemental\_files.zip) Includes:

- A sample hello afu example that executes on loaded factory image.

- A helper script to find the PCIe Root port for Intel FPGA PAC N3000.

The following table explains the differences between the two versions of the Acceleration Stack:

| Details                                        | Acceleration Stack for Runtime                                                                                     | Acceleration Stack for Development                                                                                                                                                                    |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Details                                        | runtime (rte) installer                                                                                            | development (dev) installer                                                                                                                                                                           |  |  |

| Purpose                                        | Provides necessary environment to execute the AFUs as well as allows for software development of host application. | Provides necessary environment to execute the AFUs as well as allows for software development of host application. Additionally, it also includes development environment for Intel Arria 10 GT FPGA. |  |  |

| OPAE Software Development<br>Kit (SDK) Version | 1.3.6-4                                                                                                            |                                                                                                                                                                                                       |  |  |

| Intel Quartus Prime Pro<br>Edition             | Not included or required                                                                                           | Included: Intel Quartus Prime Pro Edition software version 19.2 with IP licenses required to create a programmable Intel Arria 10 GT FPGA image.                                                      |  |  |

| Default installation location                  | N/A                                                                                                                | /home/ <username>/inteldevstack</username>                                                                                                                                                            |  |  |

Configuration installers (2x2x25G, 4x25G or 8x10G):

You can pick one of the desired configuration installer for your Intel FPGA PAC N3000.

Note: The XL710 devices are configured in different modes to support either 10G or 25G traffic. The XL710 devices cannot be configured to switch between 10G and 25G, and thus Intel recommends you to download the valid configuration installer.

Depending on the configuration on your Intel FPGA PAC N3000, the XL710 has one of the following device ID's:

| XL710 Device ID | Valid Configuration |  |  |

|-----------------|---------------------|--|--|

| 0x0d58(25G)     | 2x2x25G<br>4x25G    |  |  |

| 0x0cf8(10G)     | 8x10G               |  |  |

To identify the XL710 device ID on the Intel FPGA PAC N3000:

```

$ lspci -d :0d58

$ lspci -d :0cf8

```

Install the necessary files to update the Intel Arria 10 FPGA , Intel MAX 10 RTL and Firmware to a Root of Trust state. The files are installed at location:

- /usr/share/opae/n3000/one-time-update/<config directory>/

where <config directory> = 25G or 10G

- /usr/share/opae/super-rsu/<config directory>/

where <config directory> = 2x2x25G or 4x25G or 8x10G

#### 4.2.1. Remove Previous OPAE Packages

Remove any previous installation of OPAE or FPGA and Intel MAX 10 update package using the following:

\$ sudo yum remove opae\*

#### 4.2.2. Install the Acceleration Stack for Runtime

1. Download, extract, and change permission for the RTE installer:

```

$ tar xvzf n3000_ias_1_1_pv_rte_installer.tar.gz

$ cd n3000_ias_1_1_pv_rte_installer

$ chmod +x n3000-1.3.6-rte-setup.sh

```

2. Run the script:

```

$ sudo ./n3000-1.3.6-rte-setup.sh -y --owner <user[:group]>

```

The --owner argument allows you to change the ownership of directories to a given user. Running interactively without the -y option is not supported. For example:

```

$ sudo ./n3000-1.3.6-rte-setup.sh -y --owner john:john

```

The installation will take a few minutes to complete.

Sample output:

```

Running setup

Beginning installation

Processing group "OPAE Software"

Analyzing dependencies...

Analyzing packages to install..

error running: ['yum', 'info', 'opae-intel-fpga-driver.x86_64']

error running: ['yum', 'info', 'opae.admin.noarch']

error running: ['yum', 'info', 'opae-libs.x86_64']

error running: ['yum', 'info', 'opae-tools.x86_64']

error running: ['yum', 'info', 'opae-tools-extra.x86_64']

error running: ['yum', 'info', 'opae-devel.x86_64']

Installing OPAE Software packages..

opae-intel-fpga-driver-2.0.1-6.x86_64.rpm

opae.admin-1.0.2-3.noarch.rpm

opae-libs-1.3.6-4.x86_64.rpm

opae-tools-1.3.6-4.x86_64.rpm

opae-tools-extra-1.3.6-4.x86_64.rpm

opae-devel-1.3.6-4.x86_64.rpm Processing group "OPAE PACSign"

Analyzing dependencies...

Analyzing packages to install..

error running: ['yum', 'info', 'opae.pac_sign.x86_64']

Installing OPAE PACSign packages..

opae.pac_sign-1.0.2-3.x86_64.rpm

Extracting opae-1.3.6-4.tar.gz

```

The message *error running:* [ 'yum' , ...] in the above output is expected and can be ignored.

#### 4.2.3. Install the Acceleration Stack for Development

1. Download, extract, and change permission for the DEV installer:

```

$ tar xvzf n3000_ias_1_1_pv_dev_installer.tar.gz

$ cd n3000_ias_1_1_pv_dev_installer

$ chmod +x n3000-1.3.6-dev-setup.sh

```

2. Run the script:

```

$ sudo ./n3000-1.3.6-dev-setup.sh -y --owner <user[:group]>

```

The --owner argument allows you to change the ownership of directories to a given user. Running interactively without the -y option is not supported. For example:

```

$ sudo ./n3000-1.3.6-dev-setup.sh -y --owner john:john

```

The installation will take approximately 20 minutes to complete.

Sample output:

```

Running setup

Beginning installation

Processing group "OPAE Software"

Analyzing dependencies...

Analyzing packages to install...

error running: ['yum', 'info', 'opae-intel-fpga-driver.x86_64']

error running: ['yum', 'info', 'opae.admin.noarch']

error running: ['yum', 'info', 'opae-libs.x86_64']

error running: ['yum', 'info', 'opae-tools.x86_64']

error running: ['yum', 'info', 'opae-tools-extra.x86_64']

error running: ['yum', 'info', 'opae-devel.x86_64']

Installing OPAE Software packages..

opae-intel-fpga-driver-2.0.1-6.x86_64.rpm

opae.admin-1.0.2-3.noarch.rpm

opae-libs-1.3.6-4.x86_64.rpm

opae-tools-1.3.6-4.x86_64.rpm

opae-tools-extra-1.3.6-4.x86_64.rpm

opae-devel-1.3.6-4.x86_64.rpm

Processing group "OPAE PACSign"

Analyzing dependencies...

Analyzing packages to install... error running: ['yum', 'info', 'opae.pac_sign.x86_64']

Installing OPAE PACSign packages..

opae.pac_sign-1.0.2-3.x86_64.rpm

Extracting opae-1.3.6-4.tar.gz

Extracting pac_n3000_rtl_1.3.6.tar.gz

Installing main Quartus package: QuartusProSetup-19.2.0.57-linux.run

Installing update: quartus-19.2-0.01vc-linux.run

Source /home/<user>/inteldevstack/bin/init_env.sh to setup your environment.

Changing ownership on /home/<user>/inteldevstack

Installation done

```

The message *error running:* [ 'yum', ...] in the above output is expected and can be ignored.

Add the Intel Quartus Prime development tool to the path. This is required for AFU compilation:

```

$ source /home/<username>/inteldevstack/bin/init_env.sh

Adding /home/<username>/inteldevstack/intelFPGA_pro/quartus/bin to PATH

Adding /home/<username>/inteldevstack/intelFPGA_pro/

nios2eds/bin/gnu/H-x86_64-pc-linux-gnu/bin to PATH

Adding /home/<username>/inteldevstack/bin to PATH

```

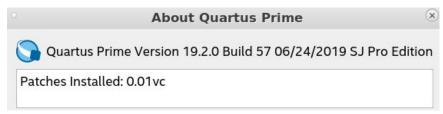

4. Verify Intel Quartus Prime installation by bringing up Intel Quartus Prime GUI and verifying the version and IP licenses:

```

$ quartus

```

a. Click **Help > About Quartus Prime** to verify Intel Quartus Prime version:

#### Figure 9. Intel Quartus Prime Version

If **patch .01vc** is not installed, then verify that init\_env.sh ran successfully.

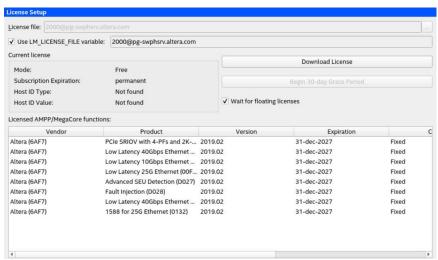

b. Click **Tools** > **License Setup** to verify IP licenses.

#### Figure 10. IP Licenses

#### 4.2.4. Verify the OPAE Installation

After executing the Acceleration Stack for Runtime or Development installer, ensure that you have successfully installed OPAE.

• Verify the OPAE package installation:

```

$ rpm -qa | grep opae

opae-intel-fpga-driver-2.0.1-6.x86_64

opae-devel-1.3.6-4.x86_64

opae-libs-1.3.6-4.x86_64

opae.admin-1.0.2-3.noarch

opae.pac_sign-1.0.2-3.x86_64

opae-tools-1.3.6-4.x86_64

opae-tools-extra-1.3.6-4.x86_64

```

Verify the OPAE driver installation:

Verify if the Linux has enumerated the Intel FPGA PAC N3000 FPGA Management Engine Device (FME):

```

$ lspci | grep 0b30

61:00.0 Processing accelerators: Intel Corporation Device 0b30

```

The above output provides the PCIe BDF (Bus: Device: Function) value for the Intel FPGA PAC. Here, the 61:00.0 indicates the bus is 61, device is 00 and function is 0. The PCIe BDF value varies based on systems, therefore your values can be different. Record this value for future use.

If the verification of OPAE installation fails, refer to Troubleshooting on page 66.

#### 4.2.5. Install the Configuration Files

The configuration (cfg) installer installs all the binary ingredients (FPGA, Intel MAX 10) required to upgrade the Intel FPGA PAC N3000 to current release version.

- 1. Install the appropriate configuration setup file (2x2x25G, 4x25G, or 8x10G).

- Filename: n3000-1.3.6-cfg-\*-setup.sh

- To change permission:

```

$ sudo chmod +x n3000-1.3.6-cfg-*-setup.sh

```

2. Run the script:

```

$ sudo ./n3000-1.3.6-cfg-*-setup.sh -y --install-dir /tmp/tmp_cfg \

--owner <user[:group]>

```

#### Sample output:

The message *error running:* [ 'yum', ...] in the above output is expected and can be ignored.

3. Verify proper installation of the one-time update (OTSU) and super-rsu files.

If you install 2x2x25G or 4x25G configuration installer, the installed files are located at

ls -l /usr/share/opae/n3000/one-time-update/25G/

ls -l /usr/share/opae/n3000/super-rsu/<config directory>/

where <config directory> = 2x2x25G or 4x25G.

If you install 8x10G configuration installer, the installed files are located at:

ls -l /usr/share/opae/n3000/one-time-update/10G/

ls -l /usr/share/opae/n3000/super-rsu/<config directory>/

where <config directory> = 8x10G.

# 4.3. Identify the Intel MAX 10 Version on your Intel FPGA PAC N3000

Run the following command and verify the output with the table below:

\$sudo fpgainfo fme

#### Table 5. Intel MAX 10 Versions

| Acceleration Stack 1.1 for Intel FPGA PAC N3000 | Intel MAX 10 NIOS Firmware (FW) | Intel MAX 10 Build |

|-------------------------------------------------|---------------------------------|--------------------|

| Production                                      | D.2.0.19                        | D.2.0.6            |

| Beta                                            | D.2.0.12                        | D.2.0.5            |

| Alpha-2                                         | D.1.0.13                        | D.1.0.14           |

| Alpha-1                                         | D.1.0.13                        | D.1.0.13           |

If your Intel FPGA PAC N3000 does not have the production version of Intel MAX 10 NIOS Firmware (FW) and Build, refer to the section: Upgrade your Intel FPGA PAC N3000 with Production Version of BMC and Intel Arria 10 Image on page 67. When you upgrade your Intel FPGA PAC N3000 from Alpha-2/Beta version to Production version, refer to the following table for Bitstream ID and PR Interface ID:

#### **Table 6.** Bitstream ID After Upgrade

| Intel FPGA Factory Partition Image |         | User Partition Image |                                                  | ge            |                      |                                                  |

|------------------------------------|---------|----------------------|--------------------------------------------------|---------------|----------------------|--------------------------------------------------|

| PAC N3000 Configuration            |         | Bitstream ID         | PR Interface ID                                  | Configuration | Bitstream ID         | PR Interface ID                                  |

| BD-NVV-<br>N3000-2                 | 2x2x25G | 0x2300041001<br>0309 | a5d72a3c-<br>c8b0-4939-912<br>c-<br>f715e5dc10ca | 4x25G         | 0x2300011001<br>0309 | f3c99413-5081<br>-4aad-<br>bced-07eb84a6<br>d0bb |

| BD-NFV-<br>N3000-1                 | 8x10G   | 0x2300001001<br>0309 | 901dd697-<br>ca79-4b05-<br>b843-8138cefa<br>2846 | 8x10G         | 0x2300001001<br>0309 | 901dd697-<br>ca79-4b05-<br>b843-8138cefa<br>2846 |

If your Intel FPGA PAC N3000 has the production version of Intel MAX 10 Firmware and Build, install the PV 1.1 Patch. When your Intel FPGA PAC N3000 is shipped with the production version, refer to the following table for Bitstream ID and PR Interface ID:

Table 7. Bitstream ID for Intel FPGA PAC N3000 shipped with Production version

| Intel FPGA<br>PAC N3000 | Factory Partition Image |                      |                                                  | User Partition Image |                      |                                                  |

|-------------------------|-------------------------|----------------------|--------------------------------------------------|----------------------|----------------------|--------------------------------------------------|

|                         | Configuration           | Bitstream ID         | PR Interface ID                                  | Configuration        | Bitstream ID         | PR Interface ID                                  |

| BD-NVV-<br>N3000-2      | 2x2x25G                 | 0x2300041001<br>030F | a5d72a3c-<br>c8b0-4939-912<br>c-<br>f715e5dc10ca | 4x25G                | 0x2300011001<br>030F | f3c99413-5081<br>-4aad-<br>bced-07eb84a6<br>d0bb |

| BD-NFV-<br>N3000-1      | 8x10G                   | 0x2300001001<br>030F | 901dd697-<br>ca79-4b05-<br>b843-8138cefa<br>2846 | 8x10G                | 0x2300001001<br>030F | 901dd697-<br>ca79-4b05-<br>b843-8138cefa<br>2846 |

#### 4.3.1. FPGA Factory Image Overview

The Intel FPGA PAC N3000 has an on-board flash with two partitions (user and factory) for storing two FPGA image files known as user image and factory image. A new Intel FPGA PAC N3000 is provided with the factory image in both factory and user partition of the flash.

After an OTSU, in 8x10G configuration, the Intel FPGA PAC N3000 is loaded with 8x10G image in both factory and user partition. While in 4x25G and 2x2x25G configurations, the Intel FPGA PAC N3000 is loaded with 2x2x25G in factory partition and 4x25G in user partition.

When the image in the user partition fails to load, the Intel FPGA PAC N3000 reverts back and boots from factory partition. This factory image loaded into the user partition provides basic functionality to demonstrate all the interfaces including Ethernet and external memory interfaces.

The factory image includes the following Intellectual Property (IP) to support in the development of Accelerator Function (AF):

- The PCIe IP core

- The Core Cache Interface protocol (CCI-P) fabric

- DDR4 memory interface controller IP

- QDR4 memory interface controller IP

- 10 or 25 GbE physical interface and MACs with pass-through connectivity between Intel Ethernet Connection C827 Retimer and Intel Ethernet Controller XL710-BM2

- FPGA Management Engine (FME)

- Nios® core to configure the Intel Ethernet Connection C827 Retimers

Figure 11. Example: Factory Image for 2x2x25G

## 5. OPAE Tools

The following OPAE tools are provided:

- fpqasupdate: This tool updates Intel MAX 10 BMC image and firmware, root entry hash, and FPGA static region (SR) user image in the user partition..

- **fpgainfo**: This tool displays FPGA information derived from sysfs files.

- fpgabist: This tool performs board self-diagnostic tests for PCIe and external memories.

- fpgadiag: This tool performs board self-diagnostic tests for network loopback.

- fpgad: This service allows for monitoring critical sensors and protect against server crashing.

- **fpgastats**: This tool provides the MAC statistics for both line side and host side.

## 5.1. Using fpgasupdate

The fpgasupdate tool updates board firmware including BMC and FPGA SR user image. This section describes how to update the FPGA SR user image. While in the upgrade process, the fpgasupdate tool securely updates the Intel MAX 10 BMC with an Intel provided signed file.

The new Intel FPGA PAC N3000 is shipped with either the 4x25G or the 8x10G factory image for 25G cards and 10G cards respectively. The following steps describe how to load FPGA images into the FPGA flash user partition. You may follow the steps to load or re-load the factory image if required.

Note:

Do not switch between 8x10G to 2x2x25G or 4x25G Intel Arria 10 images. The XL710 devices are configured in different modes to support either 10G or 25G traffic. The XL710 devices cannot be configured to switch between 10G and 25G, and thus Intel recommends you to not switch Intel Arria 10 image supporting different speed configurations.

Depending on the configuration on your Intel FPGA PAC N3000, the XL710 has one of the following device ID's:

| XL710 Device ID | Valid Configuration |  |

|-----------------|---------------------|--|

| 0x0d58(25G)     | 2x2x25G<br>4x25G    |  |

| 0x0cf8(10G)     | 8x10G               |  |

To identify the XL710 device ID on the Intel FPGA PAC N3000:

\$ lspci -d :0d58

\$ lspci -d :0cf8

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

1. Run the fpgasupdate command:

```

$ sudo fpgasupdate <FPGA Bitstream> <PCIe B:D.F>

```

Note: Running fpgasupdate involves binary file verification and writing the FPGA flash, as a result the fpgasupdate command takes approximately 40 minutes to complete.

Note: If you have programmed the static region root entry hash, then the sr\_vista\_rot\_\*\_unsigned.bin must be signed with appropriate root key and code signing key using the appropriate Hardware Security Module (HSM). For more information, refer to the Security User Guide: Intel FPGA Programmable Acceleration Card N3000.

If you want to reload the Intel provided factory image in the FPGA flash user partition, perform the following:

```

$ sudo fpgasupdate /usr/share/opae/n3000/super-rsu/<config>/\

sr_vista_rot_*_unsigned.bin [PCIe B:D.F]

```

where <config> = 2x2x25G or 4x25G or 8x10G, based on the installed configuration.

2. Perform remote system update to power cycle the Intel FPGA PAC N3000 so that the updated images are loaded into FPGAs:

```

$ sudo rsu bmcimg B:D.F

```

Note:

As a result of using the rsu command, the host rescans the PCI bus and may assign a different Bus/Device/Function (B/D/F) value than the originally assigned value. The Intel XL710 Ethernet controller should be considered unavailable during the operation. Intel recommends you to stop or pause any applications until the update is complete.

# **5.2. Using fpgainfo**

Command synopsis: fpgainfo <command> [<args>]

**Table 8.** fpgainfo Commands

| command     | args (optional) | Description                                                   |

|-------------|-----------------|---------------------------------------------------------------|

|             | help, -h        | Prints help information and exit                              |

|             | bus, -B         | Provides PCIe bus number of resource                          |

|             | device, -D      | Provides PCIe device number of resource                       |

|             | function, -F    | Provides PCIe function number of resource                     |

| errors fme  | clear, -c       | Provides/clear errors of FME                                  |

| errors port | clear, -c       | Provides/clear errors of port                                 |

| errors all  | clear, -c       | Provides/clear errors of both FME and port                    |

| power       |                 | Provides total power in watts that the FPGA hardware consumes |

| temp        |                 | Provides FPGA temperature values in degrees Celsius           |

| port        |                 | Provides information about the port                           |

| fme         |                 | Provides information about the FME                            |

|             |                 | continued                                                     |

| command | args (optional)    | Description                                                                                    |

|---------|--------------------|------------------------------------------------------------------------------------------------|

| bmc     |                    | Provides BMC sensors information                                                               |

| mac     |                    | Provides information about MAC ROM connected to FPGA                                           |

| phy     | -G <group></group> | Provides information about ethernet PHYs in FPGA. <pre><group> can be 0, 1, all.</group></pre> |

#### Example 1. fpgainfo fme

```

$ sudo fpgainfo fme

```

#### Sample output based on 2x2x25G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19 Board Management Controller, Intel MAX 10 Build version D.2.0.6 \,

//***** FME *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:b2:00.0

: 0x0b30

Device Id

: 1

Numa Node

Ports Num

: 01

Bitstream Id

: 0x23000410010309

: 0.2.3

Bitstream Version

Pr Interface Id

: a5d72a3c-c8b0-4939-912c-f715e5dc10ca

Boot Page

: user

```

#### Sample output based on 8x10G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19 Board Management Controller, Intel MAX 10 Build version D.2.0.6 \,

//***** FME *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:89:00.0

Device Id

: 0x0b30

Numa Node

: 01

Ports Num

: 0x23000010010309

Bitstream Id

Bitstream Version

: 0.2.3

: 901dd697-ca79-4b05-b843-8138cefa2846

Pr Interface Id

Boot Page

: user

```

#### Example 2. fpgainfo bmc

```

$ sudo fpgainfo bmc

```

#### Sample output based on 2x2x25G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19

Board Management Controller, Intel MAX 10 Build version D.2.0.6 //***** BMC SENSORS *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:b2:00.0

: 0x0b30

Device Id

Numa Node

: 1

: 01

Ports Num

Bitstream Id

Bitstream Version

: 0x23000410010309

: 0.2.3

: a5d72a3c-c8b0-4939-912c-f715e5dc10ca

( 1) Board Power : 74.18 Watts ( 2) 12V Backplane Current : 3.24 Amps

( 3) 12V Backplane Voltage : 12.16 Volts

: 1.19 Volts

: 1.80 Volts

(4) 1.2V Voltage

: 1.19 Volts

( 6) 1.8V Voltage

```

683040 | 2021.06.14

```

(8) 3.3V Voltage : 3.25 Volts

(10) FPGA Core Voltage : 0.90 Volts

(11) FPGA Core Current : 18.45 Amps

(12) FPGA Die Temperature : 73.50 Celsius

(13) Board Temperature : 46.50 Celsius

(14) QSFPO Supply Voltage : 0.00 Volts

(15) QSFPO Temperature : N/A

(24) 12V AUX Current : 2.85 Amps

(25) 12V AUX Voltage : 12.19 Volts

(37) QSFP1 Supply Voltage : 0.00 Volts

(38) QSFP1 Temperature : N/A

(44) PKVLO Core Temperature : 73.50 Celsius

(45) PKVLO SerDes Temperature : 73.50 Celsius

(46) PKVL1 Core Temperature : 74.00 Celsius

(47) PKVL1 SerDes Temperature : 74.50 Celsius

```

#### Note:

When the copper modules are connected to QSFP, you get N/A output for the QSFP temperature values as the QSFP EEPROM does not support copper modules. But, the OSFP EEPROM does support optical modules.

#### Sample output based on 8x10G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19 Board Management Controller, Intel MAX 10 Build version D.2.0.6 \,

//***** BMC SENSORS *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:89:00.0

Device Id

: 0x0b30

: 1

Numa Node

: 01

Ports Num

Bitstream Id

: 0x23000010010309

Bitstream Version

: 0.2.3

Pr Interface Id

(1) Board Power

: 901dd697-ca79-4b05-b843-8138cefa2846

: 70.01 Watts

(2) 12V Backplane Current : 3.06 Amps (3) 12V Backplane Voltage : 12.17 Volts (4) 1.2V Voltage : 1.19 Volts (6) 1.8V Voltage : 1.80 Volts (8) 3.3V Voltage : 3.25 Volts

( 6) 1.8V Voltage

( 8) 3.3V Voltage

( 6) 1.8V VOITage

( 8) 3.3V Voltage : 3.25 Volts

(10) FPGA Core Voltage : 0.90 Volts

(11) FPGA Core Current : 17.18 Amps

(12) FPGA Die Temperature : 79.00 Celsius

(13) Board Temperature : 43.50 Celsius

(14) QSFPO Supply Voltage : 0.00 Volts

(15) QSFPO Temperature : N/A

(24) 12V AUX Current : 2.69 Amps

: 12.19 Volts

(24) 12V AUX Current

(25) 12V AUX Voltage

: 12.19 Volts

(37) QSFP1 Supply Voltage : N/A

(44) PKVL0 Core Temperature : 76.00 Celsius

(45) PKVLO SerDes Temperature : 76.50 Celsius

(46) PKVL1 Core Temperature : 76.50 Celsius

(47) PKVL1 SerDes Temperature : 77.00 Celsius

```

#### Example 3. fpgainfo phy

```

$ sudo fpgainfo phy -B 0xb2

```

#### Sample output based on 2x2x25G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19

Board Management Controller, Intel MAX 10 Build version D.2.0.6

//****** PHY ******//

Object Id : 0xEF00000

PCIe s:b:d.f : 0000:b2:00.0

Device Id : 0x0b30

Numa Node : 1

Ports Num : 01

```

```

Bitstream Id : 0x23000410010309

Bitstream Version : 0.2.3

Pr Interface Id : a5d72a3c-c8b0-4939-912c-f715e5dc10ca

Bitstream Id

//***** PHY GROUP 0 *****//

: Line side

Direction

Speed

: 25 Gbps

Number of PHYs

: 4

//***** PHY GROUP 1 *****//

Direction

: Host side

Number of PHYs

: 40 Gbps

//***** Intel C827 Retimer *****//

Port0 25G

: Up

Port1 25G

: Up

Port2 25G

: Up

Port3 25G

: Up

Retimer A Version

: 101c.1064

Retimer B Version

: 101c.1064

```

#### Sample output based on 8x10G:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19 Board Management Controller, Intel MAX 10 Build version D.2.0.6

//***** PHY *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:89:00.0

Device Id

: 0x0b30

Numa Node

: 1

: 01

Bitstream Version : 0.2.3

Pr Interface Id

Ports Num

: 901dd697-ca79-4b05-b843-8138cefa2846

//***** PHY GROUP 0 *****//

Direction

: Line side

Speed

: 10 Gbps

Number of PHYs

: 8

//***** PHY GROUP 1 *****//

Direction

: Host side

Number of PHYs : 10 Gbps

//***** Intel C827 Retimer *****//

Port0 10G

: Up

Portl 10G

: Up

Port2 10G

: Up

: Up

Port3 10G

Port4 10G

: Up

: Up

Port5 10G

Port6 10G

: Up

: Up

Port7 10G

Retimer A Version

: 101c.1064

Retimer B Version

: 101c.1064

```

Note:

When using the 4x25G configuration, the Retimer B is held in reset to reduce power. Therefore, Retimer B firmware version is not listed (0000.0000) in the fpgainfo phy output based on 4x25G.

#### 5.3. Test PCIe and External Memories with fpgabist

Tests are included to demonstrate the performance of PCIe and external memories.

Requirements:

- OPAE tool fpgabist requires that hugepage to be set.

- For CentOS:

```

# echo 200 > /sys/kernel/mm/hugepages/hugepages-2048kB/nr_hugepages

```

— For Red Hat:

```

# echo 200 > /proc/sys/vm/nr_hugepages

```

Commands must be run as root.

Note:

The fpgabist diagnostic tool only works when the Intel supplied factory images are programmed into the Intel FPGA PAC N3000. For more information about how to reload the factory image, refer to Using fpgasupdate on page 26.

#### **Example 4. Using fpgabist**

```

# fpgabist -B 0x8a -i 0x0b30

```

Note:

Your bus (-B) value may be different.

#### **Related Information**

fpgabist Sample Output on page 77

# 5.4. Test Network Loopback using fpgadiag

The test requires use of an external traffic generator to send traffic through QSFP ports, the --side host enables loopback on the host side of the Intel Arria 10 FPGA.

```

$ sudo fpgadiag -B 0x3e -m fpgalpbk --side host --direction remote --enable

```

#### To disable:

```

$ sudo fpgadiag -B 0x3e -m fpgalpbk --side host --direction remote --disable

```

Note:

Since all four Ethernet channels in the 4x25G configuration are in QSFP0, only one QSFP port indicates linkup status through LEDs.

# 6. Sample Test: Native Loopback

This section describes how to run a memory copy test using the Intel provided FPGA factory image and hello\_fpga.c host program. The FPGA factory image includes logic to support this test and an internal register with the expected **AFU UUID**. The hello\_fpga.c only works with an FPGA image with this **AFU UUID**. The acceleration logic (NLB) in the FPGA is programmed to copy CSR\_NUM\_LINES (cache lines) from source to destination buffer on the host system. For more information refer to the Native Loopback Accelerator Functional Unit (AFU) User Guide for Intel FPGA Programmable Acceleration Card N3000.

Make sure the hugepage is allocated:

For CentOS:

```

$ sudo sh -c "echo 200 > /sys/kernel/mm/hugepages/hugepages-2048kB/\

nr_hugepages"

```

For Red Hat:

```

# echo 200 > /proc/sys/vm/nr_hugepages

```

Note: Commands must be run as root.

Extract the package:  $N3000\_supplemental\_files.zip$  which is provided as part of the Acceleration Stack installer.

```

$ unzip N3000_supplemental_files.zip

$ cd N3000_supplemental_files

$ gcc -o hello_fpga -std=gnu99 -rdynamic -ljson-c -luuid -lpthread \

-lopae-c -lm -Wl,-rpath -lopae-c hello_fpga.c

$ sudo ./hello_fpga

```

#### Sample output:

```

Using OPAE C library version '1.3.6' build '99fa5de'

Running Test

Running on bus 0x15.

dfh = 100000008000001f

id[0] = c000c9660d824272

id[1] = 9aeffe5f84570612

dfh = 2000000080000000

id[0] = a9149a35bace01ea

id[1] = ef82def7f6ec40fc

dfh = 2000000080000000

id[0] = a9149a35bace01ea

id[1] = ef82def7f6ec40fc

dfh = 2000000080000000

id[0] = a9149a35bace01ea

id[1] = ef82def7f6ec40fc

dfh = 2000000080000000

```

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

#### 6. Sample Test: Native Loopback

683040 | 2021.06.14

```

id[0] = a9149a35bace01ea

id[1] = ef82def7f6ec40fc

dfh = 1000010080001070

id[0] = f89e433683f9040b

id[1] = d8424dc4a4a3c413

Found NLBO at offset 0x28000

Done Running Test

```

Note: On a multi card system, pass PCIe bus argument -B 0x<xx>

# 7. Installing the Intel XL710 Driver

- 1. Download the i40e driver (2.9.21 version) from Intel Resource and Design Center.

- 2. Install driver as root.

```

$ tar xvzf i40e-2.9.21.tar.gz ; cd i40e-2.9.21

$ cd src

$ sudo make install

$ sudo rmmod i40e

$ sudo insmod i40e.ko

```

- 3. Download the i40e virtual function driver (3.7.53 version) from Intel Resource and Design Center.

- 4. Install driver as root.

```

$ tar xzvf iavf-3.7.53.tar.gz ; cd iavf-3.7.53

$ cd src

$ sudo make install

```

Insert the iavf kernel module to add support for virtual functions for Intel XL710:

\$ sudo insmod iavf.ko

# 7.1. Updating the Intel XL710 Firmware

To update the Intel XL710 firmware, follow these steps:

Extract the N3000\_XL710\_firmware.zip which is provided as part of the Acceleration Stack installer:

```

$ unzip N3000_XL710_firmware.zip

```

2. Change directory:

```

cd N3000_XL710_firmware/

$ export N3000_XL710_FIRMWARE=$PWD

```

3. The XL710 devices on each Intel FPGA PAC N3000 are configured during board manufacturing to support either 10G or 25G operation. You cannot change the Ethernet network operation (10G or 25G). The XL710 PCIe device ID identifies whether 10G or 25G support is configured. The device ID for 25G is 0x0d58 and for 10G is 0x0cf8 respectively.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Determine the XL710 device ID on your Intel FPGA PAC N3000 using the following commands:

```

$ lspci -d :0d58

$ lspci -d :0cf8

```

Based on the result, you will run nymupdate with the appropriate config file.

- 4. Download the NVM Update Package version 7.0: NVMUpdatePackage\_700\_Series.zip.

- 5. Extract the nvmupdate64e tool:

```

$ unzip NVMUpdatePackage_700_Series.zip

$ cd NVMUpdatePackage_700_Series/

$ tar xvzf 700Series_NVMUpdatePackage_v7_00_Linux.tar.gz

$ chmod +x 700Series/Linux_x64/nvmupdate64e

$ sudo cp 700Series/Linux_x64/nvmupdate64e $N3000_XL710_FIRMWARE/

```

6. Update the XL710:

```

$ cd $N3000_XL710_FIRMWARE/

```

For device ID: 0cf8

```

$ sudo ./nvmupdate64e -c nvmupdate_10G_0CF8.cfg

```

For device ID: 0d58

```

$ sudo ./nvmupdate64e -c nvmupdate_25G_0D58.cfg

```

- 7. A menu lists all the XL710 devices and specifies which ones have updates (only 0D58 or 0CF8 device should show **Update Available**).

- a. Enter the **Num** values (use comma to separate multiple devices)

- Hit Enter and wait. An on-screen will prompt to hit any key when programming is completed.

#### Figure 12. Step Illustration

```

[root@localhost N3000 XL710 firmware]# ./nvmupdate64e -c nvmupdate 25G 0D58.cfg

Intel(R) Ethernet NVM Update Tool

NVMUpdate version 1.33.15.1

Copyright (C) 2013 - 2019 Intel Corporation.

WARNING: To avoid damage to your device, do not stop the update or reboot or power off the

system during this update.

Inventory in progress. Please wait [*****+....]

Num Description

Ver.(hex) DevId S:B

Status

available

02) Intel(R) Ethernet 10G 4P X710/I350

6.00(6.00) 1572 00:024 Update not

rNDC

available

03) Intel(R) Ethernet Controller

6.128(6.80) 0D58 00:061 Update

XXV710 Intel(R) FPGA Programmable

available

Acceleration Card N3000 for

Networking

04) Intel(R) Ethernet Controller

6.128(6.80) 0D58 00:063 Update

XXV710 Intel(R) FPGA Programmable

available

Acceleration Card N3000 for

Networking

Options: Adapter Index List (comma-separated), [A]ll, e[X]it

Enter selection:03,04

Would you like to back up the NVM images? [Y]es/[N]o: N

Update in progress. This operation may take several minutes.

```

8. Power cycle the card using:

```

$ sudo rsu bmcimg <FPGA PCIe B:D.F>

```

In the future, you can choose to upgrade to Intel XL710 Firmware 7.3 or later and install the corresponding i40e and iavf driver. The following steps are instructive and provide guidance on how to perform firmware updates for future versions:

- Check the version compatibility between firmware and driver. Refer to the Feature Support Matrix.

- 2. Download the NVM Update package version 7.3 or above from download center.

- 3. Extract the nvmupdate64e tool:

```

$ unzip NVMUpdatePackage_*_Series.zip

$ cd NVMUpdatePackage_*_Series/

$ tar xvzf 700Series_NVMUpdatePackage_*_Linux.tar.gz

$ chmod +x 700Series/Linux_x64/nvmupdate64e

$ cd 700Series/Linux_x64/

```

4. Upgrade Intel XL710 firmware:

```

# ./nvmupdate64e

```

For more details, refer to the corresponding Readme file.

- The NVMUpdate utility returns an exit code of zero after successful completion of the update.

- 6. Power cycle the card:

```

$ sudo rsu bmcimg [PCIe B:D.F]

```

#### 7. Installing the Intel XL710 Driver

683040 | 2021.06.14

You must not use firmware version 7.1 and 7.2, since these versions do not support Intel XL710 device ID 0d58. Note:

## 8. Configuring Ethernet Interfaces

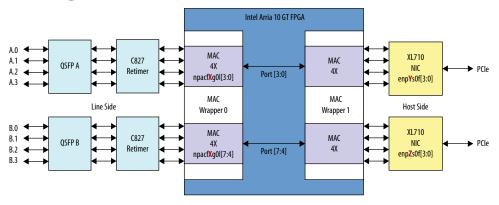

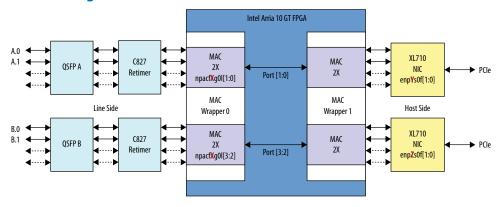

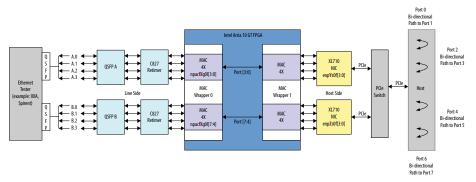

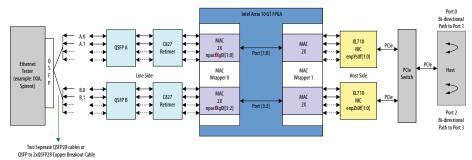

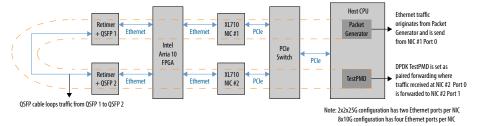

The Intel FPGA PAC N3000 contains multiple Ethernet MAC points where each point has specific naming, monitoring and configuration operations. The following figures illustrate the Ethernet data path for each network configuration.

Figure 13. 8x10G Configuration

Figure 14. 2x2x25G Configuration

Figure 15. 4x25G Configuration

The above figures show example device naming conventions for the XL710  $\exp[Y:Z]s0f[3:0]$ . Your server may have a different naming convention and numbering scheme. You will need the network logical names to use Linux tools for link configuration and monitoring. To find the network logical names of a specific Intel FPGA PAC N3000 in your server, perform the following steps:

1. List the available Intel FPGA PAC N3000 in your server using:

```

$ sudo fpgainfo fme

```

#### Sample output:

```

Board Management Controller, Intel MAX 10 NIOS FW version D.2.0.19

Board Management Controller, Intel MAX 10 Build version D.2.0.6

//***** FME *****//

Object Id

: 0xEF00000

PCIe s:b:d.f

: 0000:15:00.0

Device Id

: 0x0b30

Numa Node

: 0

: 01

Ports Num

: 0x23000410010309

Bitstream Id

Bitstream Version

: 0.2.3

: a5d72a3c-c8b0-4939-912c-f715e5dc10ca

Pr Interface Id

: user

Boot Page

```

Use the following command to find the logical name(s) of the Ethernet interfaces on that Intel FPGA PAC N3000:

```

ls -la /sys/class/net

```

#### Sample output:

```

lrwxrwxrwx. 1 root root 0 Nov 20 06:07 enp20s0f0 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:08.0/0000:14:00.0/net/enp20s0f0

lrwxrwxrwx. 1 root root 0 Nov 20 06:07 enp20s0f1 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:08.0/0000:14:00.1/net/enp20s0f1

lrwxrwxrwx. 1 root root 0 Nov 20 06:07 enp22s0f0 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:10.0/0000:16:00.0/net/enp22s0f0

lrwxrwxrwx. 1 root root 0 Nov 20 06:07 enp22s0f1 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:10.0/0000:16:00.1/net/enp22s0f1

lrwxrwxrwx. 1 root root 0 Nov 20 02:34 lo -> ../../devices/virtual/net/lo

lrwxrwxrwx. 1 root root 0 Nov 20 22:44 npacf0g0l0 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:09.0/0000:15:00.0/fpga/intel-

fpga-dev.0/intel-fpga-fme.0/pac_n3000_net.2.auto/net/npacf0g010

lrwxrwxrwx. 1 root root 0 Nov 20 22:44 npacf0g0l1 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:09.0/0000:15:00.0/fpga/intel-

fpga-dev.0/intel-fpga-fme.0/pac_n3000_net.2.auto/net/npacf0g011

lrwxrwxrwx. 1 root root 0 Nov 20 22:44 npacf0g012 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:09.0/0000:15:00.0/fpqa/intel-

```

fpga-dev.0/intel-fpga-fme.0/pac\_n3000\_net.2.auto/net/npacf0g0l2

lrwxrwxrwx. 1 root root 0 Nov 20 22:44 npacf0g0l3 -> ../../devices/

pci0000:11/0000:11:00.0/0000:12:00.0/0000:13:09.0/0000:15:00.0/fpga/intelfpga-dev.0/intel-fpga-fme.0/pac\_n3000\_net.2.auto/net/npacf0g0l3

#### For example:

This listing is example of the 8x10G network configuration. The logical device names npacf0g01[3:0] represents the Ethernet MAC wrapper 0 on the line side Intel Arria 10 FPGA. The logical device names enp[Y:Z]s0f[1:0] are the XL710 Ethernet ports.

The pac\_n3000\_net platform device driver creates the standard Linux network device interfaces for each Intel Arria 10 FPGA Ethernet MAC pair. It provides C827 retimer information for unified network status reporting. It enables use of standard Linux tools for both link configuration and monitoring.

```

$ lsmod | grep pac_n3000_net pac_n3000_net 28483 1 c827_retimer

```

## 8.1. Modifying the Interface Maximum Transmission Unit (MTU) Size

The default Maximum Transmission Unit (MTU) size for 10G FPGA MAC Wrapper 0 and Wrapper 1 is 1518 bytes. The default MTU size for 25G FPGA MAC Wrapper 0 and Wrapper 1 is 9600. The default MTU size for XL710 is 1500 bytes. You must configure FPGA MAC wrappers and XL710 to have the same MTU setting to ensure each MAC will allow your desired maximum packet size.

#### Command for configuring MTU of FPGA MAC wrapper 0:

```

$ ip link set dev npacfXgYlZ mtu <#>

<#> = desired MTU setting

```

#### Command for configuring MTU of XL710:

```

$ ip link set dev <XL710 interface name> mtu <#>

<#> = desired MTU setting

```

#### Example of current settings:

```

$ ip link show npacf0g0l0

48: npacf0g0l0: <LOWER_UP> mtu 9600 qdisc noop state UNKNOWN mode DEFAULT group

default qlen 1000

link/generic

$ ip link show enp20s0f0

52: enp20s0f0: <BROADCAST,MULTICAST,UP,LOWER_UP> mtu 1500 qdisc mq state UP mode

DEFAULT group default qlen 1000

link/ether 64:4c:36:00:17:28 brd ff:ff:ff:ff:

```

683040 | 2021.06.14

#### Example: Set MTU to 9600 for both FPGA and XL710

```

$ sudo ip link set dev npacf0g0l0 mtu 9600

$ sudo ip link set dev enp20s0f0 mtu 9600

$ ip link show npacf0g0l0

48: npacf0g0l0: <LOWER_UP> mtu 9600 qdisc noop state UNKNOWN mode DEFAULT group default qlen 1000 link/generic

$ ip link show enp20s0f0

52: enp20s0f0: <BROADCAST,MULTICAST,UP,LOWER_UP> mtu 9600 qdisc mq state UP mode DEFAULT group default qlen 1000 link/ether 64:4c:36:00:17:28 brd ff:ff:ff:ff:ff

```

#### To set the FPGA MAC Wrapper 1 MTU, use the following command:

```

$ fpgadiag -B <bus> -m fpgamac --side=host --mtu <#>

<bus> = PCIe bus of FPGA in 0xYZ format

<#> = desired MTU setting

```

#### To check FPGA MAC Wrapper 1 MTU:

```

$ sudo fpgadiag -b <bus> -m fpgamac --side=host --mtu

```

#### Sample output:

| ===== |                  |          |         |   |

|-------|------------------|----------|---------|---|

| maxin | num frame length | transmit | receive | 1 |

| mac 0 |                  | 9600     | 9600    |   |

| mac 1 | _                | 9600     | 9600    | j |

| mac 2 | 2                | 9600     | 9600    | İ |

| mac 3 | }                | 9600     | 9600    | İ |

## 8.2. Setting Forward Error Correction (FEC) Mode

The Intel FPGA PAC N3000 supports different forward error correction (FEC) modes to enhance data reliability for 25GbE network configurations. The default FEC mode is Reed Solomon FEC. The following FEC modes are available:

#### Table 9. FEC Modes

| fec_mode | Mode                                                          |  |

|----------|---------------------------------------------------------------|--|

| no       | No FEC                                                        |  |

| kr       | Fire Code Forward Error Correction (IEEE 802.3 Clause 74)     |  |

| rs       | Reed Solomon Forward Error Correction (IEEE 802.3 Clause 108) |  |

#### Note:

The configurable FEC is only supported for 2x2x25G and 4x25G network configurations. For 8x10G, the FEC setting has no impact and this operation is invalid.

#### To set FEC mode:

```

$ sudo fecmode -B <bus> <mode>

<mode> = 'no', 'kr', 'rs'

<bus> = PCIe bus of FPGA in the format "0xYZ"

```

Note:

The fecmode command causes a board level rsu event while changing FEC modes. The rsu event causes a board level reset which causes previously configured Ethernet settings to revert back to default settings. Intel recommends you first set FEC mode, then configure Ethernet and other board level settings. The rsu event may also cause the PCIe bus number to change.

#### To get FEC mode:

```

$ fecmode -B <bus>

<bus> = PCIe bus of FPGA in the format "0xYZ"

```

#### For example:

```

$ fecmode -B 0xb3

FEC mode in current driver: rs

FEC mode in current hardware: rs

$ sudo fecmode -B 0xb3 kr

reloading driver with new parameter 'kr'

performing remote system update

2019-11-14 10:00:34,121 - [[pci_address(0000:b3:00.0), pci_id(0x8086, 0x0b30)]]

performing RSU operation

2019-11-14 10:00:34,123 - [[pci_address(0000:ae:00.0), pci_id(0x8086, 0x2030)]]

removing device from PCIe bus

2019-11-14 10:00:34,124 - waiting 10 seconds for boot

2019-11-14 10:00:44,135 - rescanning PCIe bus: /sys/devices/pci0000:ae/pci_bus/

0000:ae

2019-11-14 10:00:49,119 - RSU operation complete

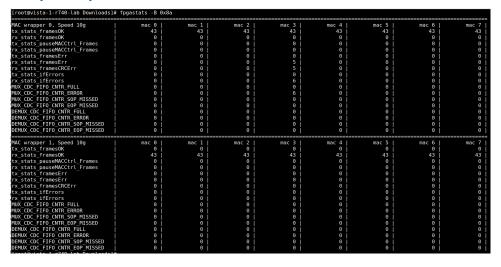

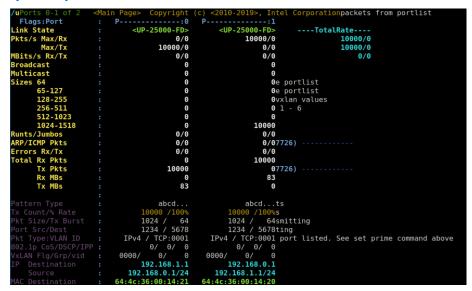

$ fecmode -B 0xb3

FEC mode in configuration: kr