# Accelerator Functional Unit Developer Guide

# Intel FPGA Programmable Acceleration Card N3000 Variants

Updated for  $Intel^{\$}$  Acceleration Stack for  $Intel^{\$}$  Xeon<sup>\$</sup> CPU with FPGAs: **1.3.1**

ID: 683190 Version: 2022.07.15

UG-20248

# Contents

| 1. About This Document                                                            |

|-----------------------------------------------------------------------------------|

| 1.1. Acronym List                                                                 |

| ,                                                                                 |

| 2. Introduction                                                                   |

| 2.1. Base Knowledge and Skills Prerequisites4         2.1.1. Considerations       |

|                                                                                   |

| 3. High Level Description                                                         |

| 3.1. Steps for Creating Your AFU6                                                 |

| 3.2. N3000 Block Diagram                                                          |

| 3.2.1. In-Line Data Path                                                          |

| 3.2.2. Supported Ethernet Network Configurations                                  |

| 3.2.4. Internal Interfaces                                                        |

| 3.3. Factory Image Description                                                    |

| 4. Creating an N3000 FPGA Design                                                  |

|                                                                                   |

| 4.1. Create New Project Directory                                                 |

| 4.2. Create four Aro Design mes                                                   |

| 4.2.2. AFU File                                                                   |

| 4.2.3. QSF File                                                                   |

| 4.2.4. SDC File                                                                   |

| 4.3. Build with make                                                              |

| 4.4. Check Timing 41                                                              |

| 4.5. Loading Your AFU into the Intel FPGA PAC N300043                             |

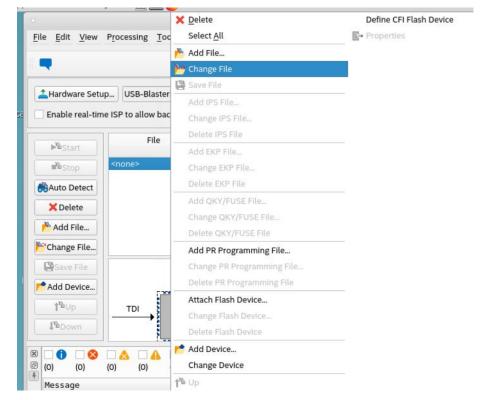

| 4.5.1. Loading Your FPGA Image with JTAG44                                        |

| 4.5.2. AFU Clocks                                                                 |

| 4.5.3. Creating an AFU with High Level Synthesis (HLS)                            |

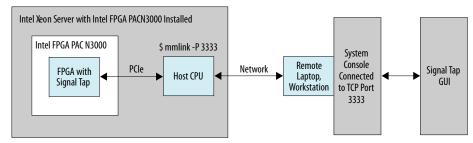

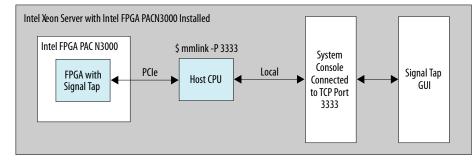

| 5. Capturing Signals in AFU with Signal Tap76                                     |

| 5.1. Adding Signal Tap to the Design77                                            |

| 5.2. Loading FPGA Image86                                                         |

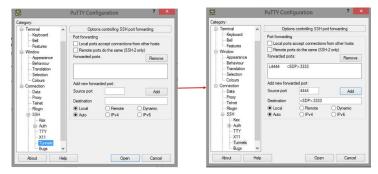

| 5.3. Set Up Connections                                                           |

| 5.4. How to Exit from the Debug Session                                           |

| 5.5. Troubleshooting Remote Debug Connections                                     |

| 6. Document Revision History for the Accelerator Functional Unit Developer Guide: |

| Intel FPGA Programmable Acceleration Card N3000 Variants                          |

# **1. About This Document**

This document serves as a high level guide for system architects and hardware developers in developing Accelerator Functional Units (AFUs) for both:

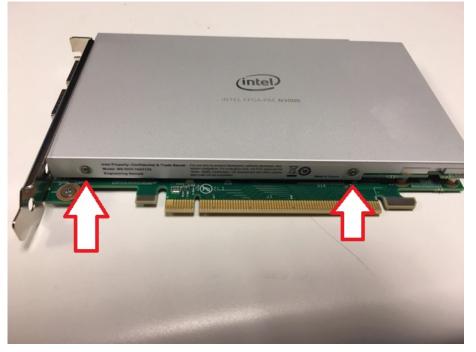

- Intel FPGA Programmable Acceleration Card N3000

- Intel FPGA Programmable Acceleration Card N3000-N

This document is organized as follows:

- 1. Document Introduction and required background knowledge

- 2. High Level Description

- 3. Developing AFUs

- 4. Debugging AFUs

# 1.1. Acronym List

| Acronym                                                                  | Expansion                                                | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel FPGA PAC<br>N3000-N (referred<br>to as N3000 for this<br>document) | Intel FPGA Programmable<br>Acceleration Card N3000-<br>N | Intel FPGA Programmable Acceleration Card N3000-N is a full-duplex 100 Gbps in-system re-programmable acceleration card for multi-workload networking application acceleration.                                                                                                                                   |

| AFU                                                                      | Accelerator Functional<br>Unit                           | Hardware Accelerator implemented in FPGA logic which offloads a computational operation for an application from the CPU to improve performance.                                                                                                                                                                   |

| AF                                                                       | Acceleration Function                                    | Compiled Hardware Accelerator image implemented in FPGA logic that accelerates an application.                                                                                                                                                                                                                    |

| АРІ                                                                      | Application Programming<br>Interface                     | A set of subroutine definitions, protocols, and tools for building software applications.                                                                                                                                                                                                                         |

| DPDK                                                                     | Data Plane Development<br>Kit                            | The Data Plane Development Kit consists of libraries to accelerate packet processing workloads running on many CPU architectures, including x86, POWER and ARM processors. DPDK runs mostly on Linux with a FreeBSD port available for a subset of DPDK features. The Open Source BSD License DPDK licenses DPDK. |

| FIU                                                                      | FPGA Interface Unit                                      | FIU is a platform interface layer that acts as a bridge between platform interfaces like PCIe* and AFU-side interfaces such as CCI-P.                                                                                                                                                                             |

| OPAE                                                                     | Open Programmable<br>Acceleration Engine                 | The OPAE is a set of drivers, utilities, and API's for managing and accessing AFs.                                                                                                                                                                                                                                |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

# 2. Introduction

Before using this guide, refer to the user guide that corresponds with your card: Intel<sup>®</sup> Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000 or Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000-N. Both user guides provide an overview of the capabilities of the Intel FPGA PAC N3000 and Intel FPGA PAC N3000-N, referred to as N3000 throughout this document. Both user guides provide instructions for installation and setup of hardware and software components of the stack, including the Open Programmable Acceleration Engine (OPAE) tools used in running diagnostic tools and remotely loading FPGA images. It is essential to familiarize yourself with the concepts developed and to complete the installation and setup procedures covered in both user guides.

To perform AFU development, install the Intel Acceleration Stack for Development as described in the user guide that corresponds with your card: *Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000* or *Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000-N*.

# **Related Information**

- Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000

- Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000-N

# **2.1. Base Knowledge and Skills Prerequisites**

The Intel Acceleration Stack is an advanced application of FPGA technology. The platform-level complexity has been abstracted away for the AFU developer by the inclusion of all interfaces in the FPGA factory image and a standard Core Cache Interface (CCI-P) interface for host connectivity to your AFU.

This guide assumes the following FPGA logic design-related knowledge and skills:

- FPGA compilation flows including the Intel Quartus<sup>®</sup> Prime Pro Edition design flow.

- Static Timing closure, including familiarity with the Timing Analyzer tool in Intel Quartus Prime Pro Edition, applying timing constraints, Synopsys\* Design Constraints (.sdc) language and Tcl scripting, and design methods to close on timing critical paths.

- RTL and coding practices to create synthesized logic.

- High level synthesis (HLS) and Platform Designer design entry tools are supported.

- RTL simulation tools.

- Signal Tap Logic Analyzer tool in the Intel Quartus Prime Pro Edition software.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

# 2.1.1. Considerations

If you are familiar with other Intel Acceleration Products, there are similarities and differences between the Intel Programmable Acceleration Card with Intel Arria $^{(\! R)}$  10 GX FPGA operation:

- Similarities:

- CCI-P interface between user logic and Intel supplied PCIe interface

- OPAE kernel driver and tools for diagnostics and remote debugging

- FPGA region dedicated to OPAE management logic

- Differences:

- Partial reconfiguration is not supported

- The FPGA is a flat design loaded by on board flash

- User must include encrypted blocks for board management

- ASE simulation is not supported

- Automated simulation and synthesis environment set up are not supported

- *Note:* The OPAE version for the N3000 is not compatible, with previous and current versions of OPAE supporting Intel PAC with Intel Arria 10 GX FPGA.

# **3. High Level Description**

The N3000 provides you with a rapid design methodology for creating complex FPGA and Intel Xeon<sup>®</sup> networking applications. You are provided the following:

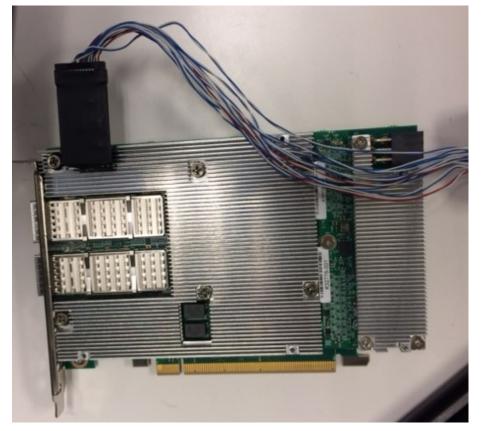

- An Intel certified board with Intel Arria 10 GT FPGA, PCIe interfaces, external memories, board management controller and Ethernet network interface devices.

- FPGA factory image design demonstrating all interfaces.

- Software tools for running board diagnostics with FPGA factory image, performing FPGA remote update, and reading board sensors.

- Internal FPGA Nios<sup>®</sup> II controller and firmware for Ethernet re-timer provisioning and board control functions. You must include this block in your design.

- The FPGA design flow, which supports flexible Ethernet data flow configurations supporting your developed packet processing functions.

The Intel supplied board, FPGA IP blocks and software allow you to focus on your value added functionality.

# **3.1. Steps for Creating Your AFU**

The following steps are suggested for designing a custom FPGA application for the N3000:

- 1. Become familiar with the board and FPGA block diagrams, interfaces and code provided within the N3000 factory image.

- 2. Review the *Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual.* You must follow the interface requirements and include required registers in your design for proper N3000 operation.

In addition, the OPAE Basic Building Blocks wiki provides CCI-P tutorials and basic building blocks (BBB) for interfacing your AFU. You are strongly encouraged to review this resource. The Memory Properties Factory BBB is an essential component for transaction ordering in AFUs requiring more complex host interfacing functions.

- 3. Define and plan your FPGA application.

- 4. Copy the Initial\_Shell\_AFU files and directory structure. This directory structure is the starting point for your design.

- 5. Implement your FPGA application. You can use one or a combination of the following design entry methods:

- a. RTL (System Verilog/VHDL)

- b. Platform Designer

- c. HLS

Note: Existing design blocks can be added as required.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

- 6. Implement host software code.

- 7. Simulate your design at the unit level.

- 8. Create timing constraints files.

- 9. Update the Intel Quartus Prime Settings File (afu.gsf) to add your new blocks.

- 10. Compile, synthesize, place and route your new design using provided makefile.

- 11. Validate timing closure.

- 12. Validate power consumption.

- 13. The provided makefile compilation script includes a post-compilation script that creates a raw binary file.

- 14. The raw binary file is used as an input to the Intel Acceleration Stack utility PACSign. PACSign adds a required header to the raw binary file. The output file from PACSign is validated by the N3000 Intel MAX<sup>®</sup> 10 Root of Trust for storage in the N3000 flash storage.

- 15. Flash the binary file produced by PACSign into FPGA flash using fpgasupdate.

- 16. Use the rsu utility to load the new FPGA binary file from flash into the FPGA.

- 17. If needed, use the Signal Tap tool to diagnose and resolve issues.

### **Related Information**

Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual

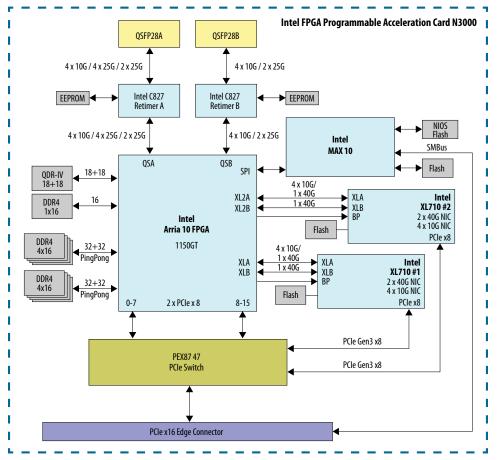

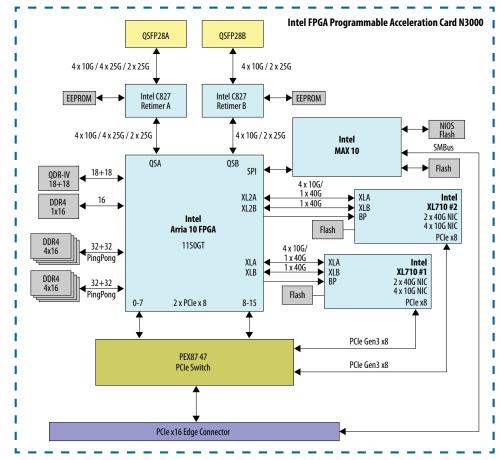

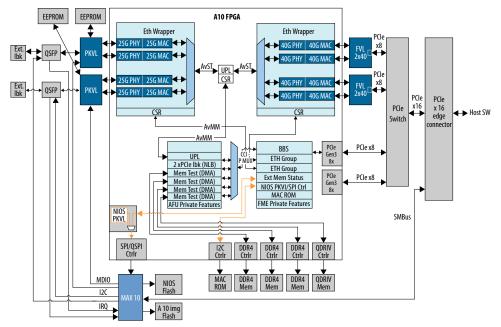

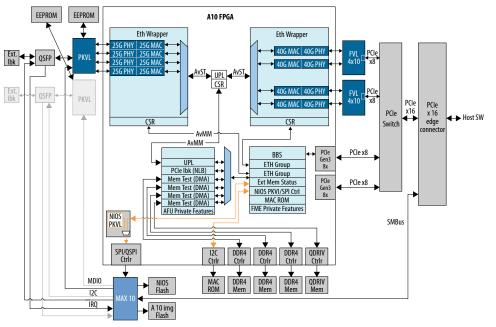

# 3.2. N3000 Block Diagram

The board level N3000 block is shown below:

Figure 1. N3000 Block Diagram

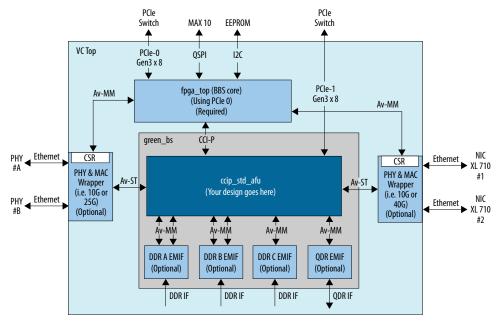

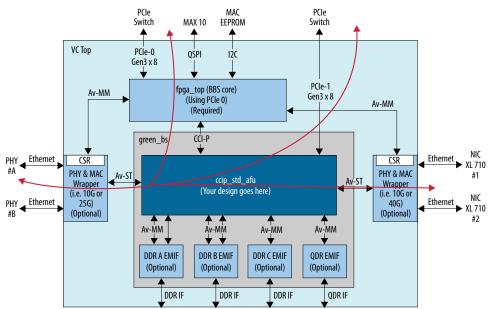

As can be seen in Figure 1 on page 8, the Intel Arria 10 FPGA is central to data and control flow. Within the Intel Arria 10 FPGA, there are both data and control IP cores that are required for the board to work properly. You must include these required IP cores in your designs. Figure 2 on page 9 illustrates the Intel provided required and optional blocks as well as the  $ccip_std_afu$  block where your design is instantiated.

### Figure 2. ccip\_std\_afu Block

# 3.2.1. In-Line Data Path

The N3000 supports multiple data path options. Your application can use one or more of these data options.

Ethernet data can be processed in-line where traffic traverses: QSFP > Intel Arria 10 FPGA > Intel Ethernet Controller XL710-BM2 NIC > Host and/or QSFP > Intel Arria 10 FPGA > Host. These data paths are shown below:

## Figure 3. Data Path

Data can also be processed in a look-aside configuration where the data comes into the Intel Arria 10 FPGA from the host PCIe interface, the FPGA processes the data and then sends the data back to the host through the PCIe connection. Some examples of look-aside processing are compression/de-compression and encryption/decryption.

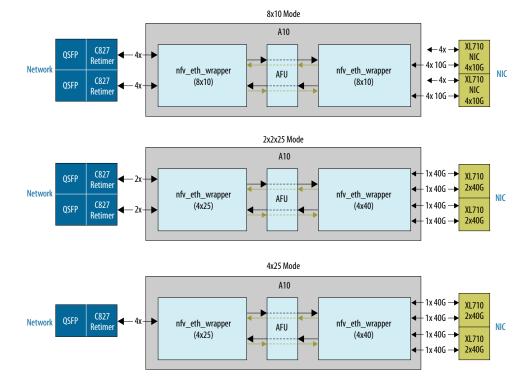

# **3.2.2. Supported Ethernet Network Configurations**

| Network<br>Configuration | QSFP28 A  | QSFP28 B  | Intel XL710 #1 | Intel XL710 #2 | Supported Board OPN              |

|--------------------------|-----------|-----------|----------------|----------------|----------------------------------|

| 8 x 10GbE                | 4 x 10GbE | 4 x 10GbE | 4 x 10GbE      | 4 x 10GbE      | BD-NFV-N3000-1                   |

| 2 x 2 x 25GbE            | 2 x 25GbE | 2 x 25GbE | 2 x 40GbE      | 2 x 40GbE      | BD-NFV-N3000-2<br>BD-NFV-N3000-N |

| 4 x 25GbE                | 4 x 25GbE | Not Used  | 2 x 40GbE      | 2 x 40GbE      | BD-NFV-N3000-2<br>BD-NFV-N3000-N |

The N3000 has three network configurations:

- 2 QSFP ports where each QSFP supports 4 10 GbE lanes this configuration is referred to as 8 X 10 G

- 2 QSFP slots where each QSFP supports 2 25 GbE lanes this configuration is referred to as 2 x 2 x 25 G

- 1 QSFP port where 4 25 GbE lanes are supported. This configuration is referred to as 4 x 25 G

*Note:* The above network configurations are the only ones supported.

The fpga\_top block contains a Nios II processor and firmware that configures the network settings for the Intel C827 Ethernet re-timer device. This Nios II firmware is not user editable.

The Intel Ethernet Controller XL710-BM2 network interface controller (NIC) is configured during board manufacturing to be either 10G or 40G. You cannot change the Intel Ethernet Controller XL710-BM2 NIC to switch between 10G and 40G. If your data path requires the Intel Ethernet Controller XL710-BM2 NIC, then you cannot switch between 10G and 25G network configurations. You can switch FPGA images between any of the supported network configurations.

# **3.2.3. Provided Files**

The N3000 Acceleration Stack for Development software release provides the files for an example design. You can review this file set as a learning step for the creation of your design.

To access the files, go to your N3000 software installation directory and enter the following commands:

```

$ cd <N3000 Installation Directory>/inteldevstack/rtl/n3000_1_3_v1.5.7

$ export N3000_EXAMPLE_ROOT=$PWD

```

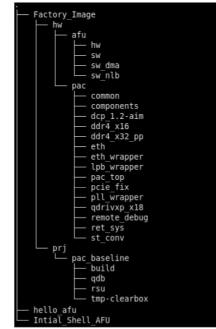

# **3.2.3.1. Directory Structure**

The supplied FPGA files are a combination of clear text and encrypted files.

The directory structure of the supplied source files is shown below:

Directory Structure of the Factory\_Image sub directory:

- /hw/afu this is where the AFU factory image example is located

- /hw Sub directory with clear text RTL, afu.qsf and afu.sdc

- /sw Sub directory with example software code

- /hw/pac this is where Ethernet MAC, external memory interface, and encrypted FIM is included

- /prj/pac\_baseline Intel Quartus Prime project files

- /prj/pac\_baseline/build programming files and build reports after

compilation completes

- At the top of the directory tree is the Makefile used in compiling the project.

- The hello\_afu sub directory contains a simple example AFU illustrating design points. The Initial\_Shell\_AFU contains a starting directory structure for your new AFU design.

# 3.2.4. Internal Interfaces

The ccip\_std\_afu module has the following interfaces:

- 1. Core Cache Interface (CCI-P) This is an FPGA Host PCIe interface required for OPAE stack operation.

- 2. Ethernet interface This interface provides each Ethernet interface as individual or Multiplexed Avalon<sup>®</sup> streaming interface bus or buses.

- 3. Local Memory Each external memory has an Avalon memory-mapped interface interface.

- 4. PCIe Optional secondary PCIe interface can be included if needed in your AFU for additional host - FPGA data transfer capability.

# 3.2.4.1. Core Cache Interface (CCI-P)

The N3000 uses the CCI-P interface for compatibility with the OPAE software stack and drivers. The N3000 has the FIU capabilities of the Intel PAC with Intel Arria 10 GX FPGA as shown in the Comparison of FIU Capabilities section of the Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual.

Note: You must develop a detailed understanding of the CCI-P Interface as described in the CCI-P Interface section of the Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual.

| Signal              | Width | Direction | Description                                                                                        |

|---------------------|-------|-----------|----------------------------------------------------------------------------------------------------|

| pClk                | 1     | Input     | 200 MHz system clock. All CCI-P signals are synchronous to this signal.                            |

| pClkDiv2            | 1     | Input     | 200 MHz system clock. This signal is a copy of ${\tt pClk}.$ Please ignore name                    |

| pClkDiv4            | 1     | Input     | 200 MHz system clock. This signal is a copy of ${\tt pClk}.$ Please ignore name.                   |

| uClk_usr            | 1     | Input     | User clock – Default = 312.5 MHz clock. To use this clock, set<br>USE_BBS_CLK=1 in make settings.  |

| uClk_usrDiv2        | 1     | Input     | User clock – Default = 156.25 MHz clock. To use this clock, set<br>USE_BBS_CLK=1 in make settings. |

| G_CLK100            | 1     | Input     | 100 MHz global reference clock, for optional PCIe IP core or additional PLLs if needed             |

| t_if_ccip_Rx        | struc | Input     | CCI-P data input structure defined in ccip_if_pkg.sv                                               |

| t_if_ccip_Tx        | struc | Output    | CCI-P data output structure defined in ccip_if_pkg.sv                                              |

| pck_cp2af_softReset | 1     | Input     | Active high reset. Synchronous with ${\tt pClk}$ asserted for 256 clock cycles.                    |

| pck_cp2af_pwrState  | 2     | Input     | Present, but not used                                                                              |

| pck_cp2af_error     | 1     | Input     | Present, but not used                                                                              |

The N3000 has the following signals in the CCI-P interface:

The CCI-P clocks: pClk, pClkDiv2, pClkDiv4, uClk\_usr, and uClk\_usrDiv2 do not allow you to change frequencies. If your AFU requires a different clock frequency, then instantiate a new PLL and use the G CLK100 as a PLL reference clock.

# **Related Information**

Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) **Reference Manual**

# 3.2.4.1.1. FPGA Internal Register Access

Access to internal FPGA registers with the PCIe 0 CCI-P interface uses Memory Mapped I/O (MMIO) access. You may use the following types of internal registers:

- Direct access

- Indirect access

Direct access registers consist of MMIO addressable registers. The provided example design hello\_afu.sv illustrates direct access registers.

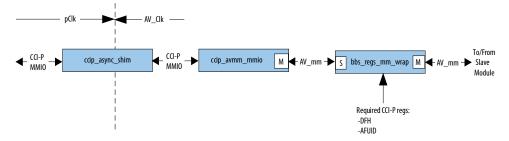

The CCI-P protocol MMIO address space is limited to 256 kB. The indirect access registers provide a mechanism to address larger areas by including control and response registers for extended slave addressing. AFU designers may use the provided ccip\_to\_avmm module to provide indirect access for your Avalon memory-mapped interface slave modules. The ccip\_to\_avmm module block diagram is shown below:

### Figure 4. CCI-P to Avalon memory-mapped interface Block

As can be seen in this block diagram, this module consists of the following:

- ccip\_async\_shim CCI-P to and from Avalon clock domain crossing

- ccip\_avmm\_mmio converts MMIO to and from Avalon memory-mapped interface

- bbs\_regs\_mm\_wrap contains CCI-P required DFH and AFU ID registers and indirect command and status registers

The indirect command and status registers are defined as follows:

### Table 1. Control Register

| Field Name | Range   | Access | Description                                                                                    |

|------------|---------|--------|------------------------------------------------------------------------------------------------|

| cmd        | [63:62] | RW     | Command for slave:<br>0x0 - NOP<br>0x1 - indirect read request<br>0x2 - indirect write request |

| addr       | [61:32] | RW     | Slave address                                                                                  |

| Write data | [31:0]  | RW     | Slave write data                                                                               |

For an indirect write request:

1. Write the following to the Control register:

Send Feedback

- cmd = 0x2•

- addr .

- Write data

- 2. Poll on the RW valid field of the Status register for RW valid = 1 to verify that the write is successful.

For an indirect read request,:

- 1. Write the following to the Control register::

- cmd = 0x1

- addr

- 2. Poll on the RW valid field of the Status register for RW valid = 1 to verify that the RD Data field contains valid data.

### BBS\_regs\_mm\_wrap Access Behavior

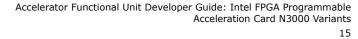

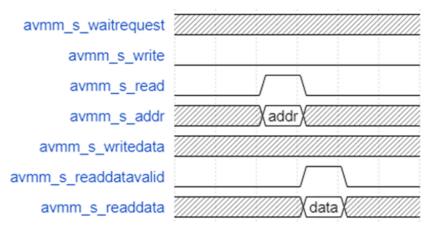

The following figures show the bbs\_regs\_mm\_wrap upstream Avalon memorymapped interface slave to downstream Avalon memory-mapped interface slave waveforms for indirect write and read operations.

Pay attention to the downstream Avalon memory-mapped interface master waveforms Note: for proper operation with your slave module.

### Indirect Write and Read Requests with Non-Blocking Access

The back pressure signal (avmm\_s\_waitrequest) is not used from the indirect access module to the CCI-P; and a write (WR) or read (RD) transaction can start at any time, but must complete in the next clock cycle.

Figure 5 on page 15 and Figure 6 on page 16 demonstrate this behavior:

# Figure 5. Avalon memory-mapped interface Waveforms for Indirect Write Request with NONBLOCKING\_ACCESS\_EN = 1

| avmm_s_waitrequest   |                                           |          |                  |         | İ/////       |                                              |

|----------------------|-------------------------------------------|----------|------------------|---------|--------------|----------------------------------------------|

| avmm_s_write         |                                           |          |                  | /       |              |                                              |

| avmm_s_read          |                                           |          |                  | /       |              |                                              |

| avmm_s_addr          |                                           | ad       | dr)/////         |         |              |                                              |

| avmm_s_writedata     |                                           | /////wr_ | _c <i>X/////</i> |         | ///////      |                                              |

| avmm_s_readdatavalid |                                           |          |                  |         |              |                                              |

| avmm_s_readdata      |                                           |          |                  |         | İ/////       |                                              |

|                      |                                           |          |                  |         |              |                                              |

| avmm_m_waitrequest   |                                           |          |                  | 1       |              | <i>\////////////////////////////////////</i> |

| avmm_m_write         |                                           |          |                  | 1       |              |                                              |

| avmm_m_read          |                                           |          |                  |         |              |                                              |

| avmm_m_addr          |                                           |          |                  | addr    |              | X/////////////////////////////////////       |

| avmm_m_writedata     |                                           |          | X                | // data |              | X/////////////////////////////////////       |

| avmm_m_readdatavalid |                                           |          |                  |         |              |                                              |

| avmm_m_readdata      | ·<br>//////////////////////////////////// |          |                  |         | ·<br>/////// |                                              |

#### Avalon memory-mapped interface Waveforms of Indirect Read Request with Figure 6. NONBLOCKING\_ACCESS\_EN = 1

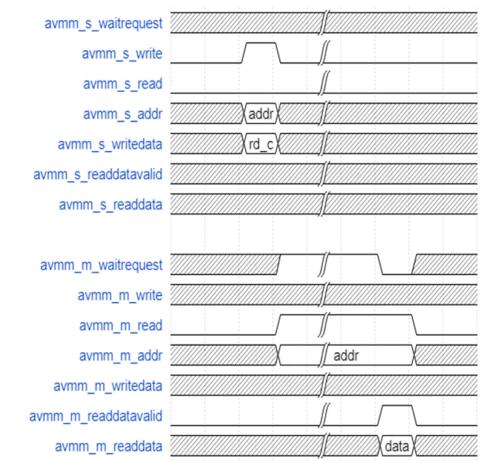

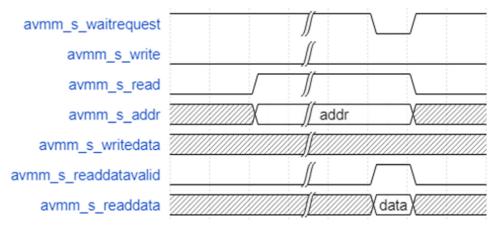

# Write and Indirect Read Requests with Blocking Access

The back pressure signal (avmm\_s\_waitrequest) is always set to '1' in the NOP state; and a write (WR) or read (RD) transaction can start when avmm\_s\_waitrequest = 1, but cannot finish until avmm\_s\_waitrequest != 0.

Figure 7 on page 17 and Figure 8 on page 18 demonstrate this behavior:

3. High Level Description 683190 | 2022.07.15

## **Figure 7.** Write Request with NONBLOCKING\_ACCESS\_EN = 0

# avmm\_s\_waitrequest avmm\_s\_write avmm\_s\_read addr avmm\_s\_addr avmm s writedata / rd\_c avmm\_s\_readdatavalid avmm\_s\_readdata avmm\_m\_waitrequest avmm\_m\_write avmm m\_read addr avmm\_m\_addr avmm\_m\_writedata avmm m readdatavalid avmm\_m\_readdata data

## Figure 8. Waveform of Indirect Read Request with NONBLOCKING\_ACCESS\_EN = 0

# Avalon memory-mapped interface Master Response to a Read Request with Non-Blocking and Blocking Access

You can read data on the bus for the following conditions:

- When AVMM\_MASTER\_READDATAVALID\_EN = 1 and avmm\_m\_readdatavalid are valid

- When AVMM\_MASTER\_READDATAVALID\_EN = 0 and (!avmm\_m\_waitrequest & avmm\_m\_read) are valid

Figure 9 on page 18 and Figure 10 on page 19 demonstrate this behavior:

# Figure 9. Avalon memory-mapped interface Master Response to a Read Request with NONBLOCKING\_ACCESS\_EN = 1

# **Figure 10.** Avalon memory-mapped interface Master Response to a Read Request with NONBLOCKING\_ACCESS\_EN = 0

### **Related Information**

- Ethernet MAC Wrapper Register Access on page 30

- Ethernet MAC Wrapper Register Access on page 30

- CCI-P Async Shim Basic Building Block

- CCI-P Basic Building Block Wiki

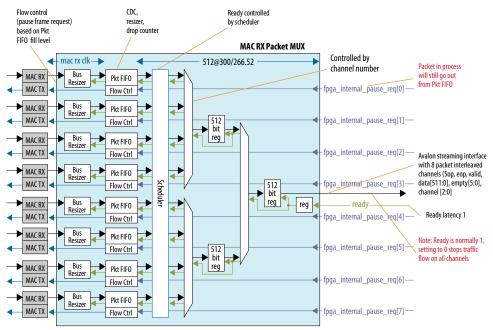

# **3.2.4.2. Ethernet Interface**

The N3000 has Ethernet MAC IP cores to provide Ethernet receive packet delineation and transmit packet origination. The Ethernet MACs are instantiated in both the network interface and the N3000 Intel Ethernet Controller XL710-BM2 NIC interface, as shown below:

#### Figure 11. **Instantiated Ethernet MACs**

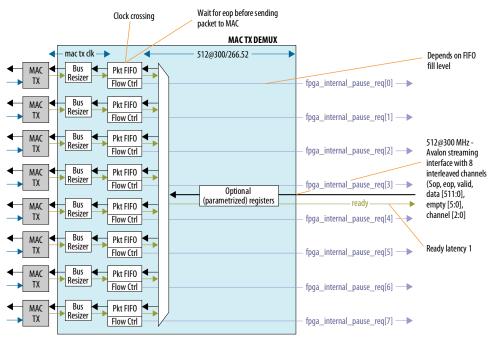

The nfv\_eth\_wrapper module is configurable by Verilog parameters for the type of Ethernet interface (10, 25 or 40 G), number of interfaces and aggregated or disaggregated style of the AFU interface. The setting of these Verilog parameters is performed by the Makefile option settings described in the Build with make section. The nfv eth wrapper module includes the following:

- Ethernet MAC

- PLL

- Multiplex/De-Multiplex blocks

The AFU Ethernet interface has three options with the following properties:

## **Aggregated:**

- 1. One Avalon streaming interface bus aggregating all traffic from each Ethernet interface

- 2. Common clock

- 3. Each Ethernet channel is identified by Avalon streaming interface channel identifier

- 4. Full Ethernet MAC statistics provided

The aggregated option allows your AFU to have a common packet processing pipeline. The aggregated option uses more FPGA resources and introduces delay from a packet buffer.

#### Figure 12. **8x10G Multiplexor**

#### Figure 13. **8x10 De-Multiplexor**

Send Feedback

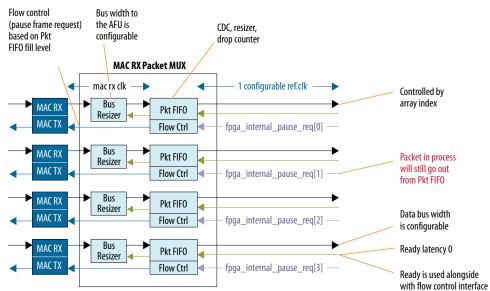

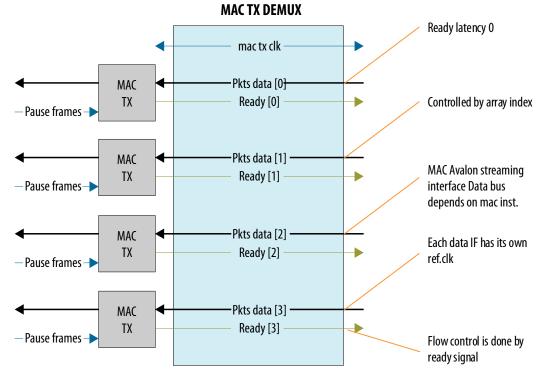

## **Disaggregated:**

intel

- 1. Each Ethernet MAC has an Avalon streaming interface bus provided as an array of Avalon streaming interface. Each channel is identified by array index.

- 2. Received packets with errors (CRC, length errors) are dropped from MAC.

- 3. Egress FIFO saturation based flow control is provided to AFU.

- 4. One common clock is used by AFU logic.

The disaggregated configuration reduces FPGA resources removing the multiplex/demultiplex blocks.

# Figure 14. MAC RX Packet MUX

### Figure 15. MAC TX DEMUX

Accelerator Functional Unit Developer Guide: Intel FPGA Programmable Acceleration Card N3000 Variants

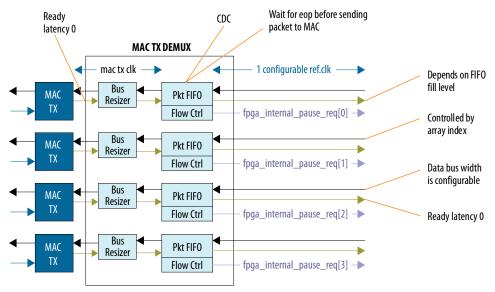

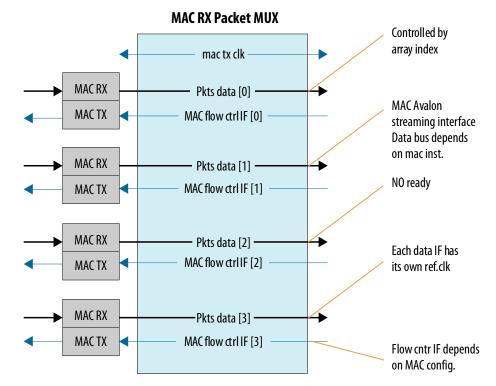

# **Lightweight Mode**

- 1. Disaggregated Avalon streaming interface interfaces from each MAC.

- 2. MUX function passes received traffic directly to the AFU.

- 3. The AFU must control the data stream by removing frames with errors and controlling the flow.

- 4. Each MAC interface has a separate clock.

- 5. No Ethernet statistics provided in Ethernet MACs.

*Note:* The Lightweight mode is not supported for 10G applications.

### Figure 16. MAC RX Packet MUX

# Figure 17. MAC TX DEMUX

# **Related Information**

Build with make on page 37

# **3.2.4.3. Ethernet MAC**

The 25 GbE MAC IP core is documented in the 25G Ethernet Intel Arria 10 FPGA IP User Guide. The N3000 configures the 25 GbE MACwith the following parameters set:

# Table 2. 25G MAC IP Setting

| Parameter                      | IP Core parameter setting       |

|--------------------------------|---------------------------------|

| Ready Latency                  | 0                               |

| Enable RS-FEC                  | Off                             |

| Enable flow control            | On                              |

| Enable link fault generation   | On                              |

| Enable preamble pass through   | Off                             |

| Enable TX CRC pass through     | Off                             |

| Enable MAC statistics counters | On<br>Off for Light weight mode |

| Enable IEEE 1588               | Off                             |

The Intel C827 Re-timer performs FEC functionality, therefore the A10 Ethernet MAC does not have RS-FEC enabled.

The 10 GbE MAC IP core is documented in: Low Latency Ethernet 10G MAC Intel Arria 10 FPGA IP Design Example User Guide

The 40 GbE MAC IP core is documented in: Low Latency 40-Gbps Ethernet IP Core User Guide

The 40 and 10 GbE MAC IP core are set with the following parameters:

### Table 3.40G MAC IP Setting

| Parameter                        | IP core parameter setting |

|----------------------------------|---------------------------|

| Enable SyncE                     | Off                       |

| PHY reference                    | 644.53125MHz              |

| Use external TX MAC PLL          | On                        |

| Flow control mode                | Standard flow control     |

| Average inter-packet gap         | 12                        |

| Enable 1588 PTP                  | Off                       |

| Enable link fault generation     | On                        |

| Enable TX CRC insertion          | On                        |

| Enable preamble pass through     | Off                       |

| Enable alignment EOP on FCS word | On                        |

| Enable TX statistics             | On                        |

| Enable RX statistics             | On                        |

| Enable strict SFD checking       | Off                       |

# 3.2.4.4. 40G - 25G Gearbox

For 25 GbE operation, the Intel Arria 10 FPGA provides a gearbox that rate adjusts between the 25 GbE network interface and the Intel Ethernet Controller XL710-BM2 NIC 40 GbE interface.

Received 25 GbE traffic is written into a per port 32 kB Intel Arria 10 FPGA FIFO. The FIFO data is read out on packet boundaries using a 40 GbE rate where an entire packet is transferred to the Intel Ethernet Controller XL710-BM2 NIC. The Intel Arria 10 FPGA extends the interframe packet gap to the Intel Ethernet Controller XL710-BM2 NIC such that the data rate is 40 Gb, however the number of packets transferred is determined by the number of packets received from the 25 GbE network port.

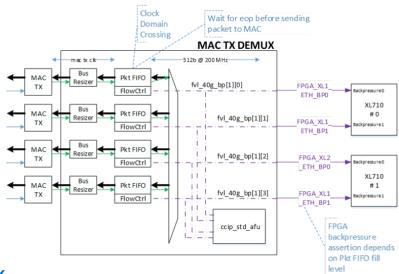

The Intel Ethernet Controller XL710-BM2 NIC sends Ethernet traffic to the Intel Arria 10 FPGA over a 40 GbE path. The Intel Arria 10 FPGA buffers the 40 GbE traffic in a 32 kB packet-based FIFO. If the Intel Arria 10 FPGA FIFO exceeds half fill level, then the Intel Arria 10 FPGA asserts a backpressure external pin, signaling the Intel Ethernet Controller XL710-BM2 NIC to extend the interframe packet gap. Once the Intel Arria 10 FPGA FIFO capacity drops to a quarter of capacity, then the backpressure external pin is de-asserted. This extended interframe packet gap reduces the packet rate such that the resulting data rate is 25 Gb. The backpressure signals are connected to the ccip\_std\_afu module. The Intel Ethernet Controller XL710-BM2 NIC to Intel Arria 10 FPGA data flow is shown in this figure:

# Figure 18.

# **MAC TX DEMUX**

# 3.2.4.5. External Memory Interfaces

The N3000 has the following external memory interfaces as shown in the board block diagram below:

- DDR4 2133 Mb/s total 9 GB

- DDR4A and DDR4B each 4 GB banks

- 64-bit wide

- Ping-Pong physical interface

- DDR4C 1 GB bank

- 16-bit wide

- QDR4 1066 MHz 144 Mb

- 8M x 18

### **Related Information**

External Memory Interfaces Intel Arria 10 FPGA IP User Guide

# 3.2.4.5.1. DDR4A and DDR4B

Both DDR4A and DDR4B use the Ping Pong PHY described in the *Intel Arria 10 EMIF Ping Pong PHY Description* section of the *External Memory Interfaces Intel Arria 10 FPGA IP User Guide*.

The Ping Pong PHY is physically implemented in the board design. The Ping Pong PHY design has two independent memory controllers per DDR4 interface where your interface consists of two Avalon memory-mapped interface interfaces. See DDR4A user interface below (please note, DDR4B is identical).

| ccip_std_afu<br>Direction | Width   | Signal Name                | Description                                                                                                                          |

|---------------------------|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| DDR4A_0 Interface         |         |                            |                                                                                                                                      |

| input                     |         | ddr4a_avmm_0_clk           | 266 MHz clock sourced from EMIF                                                                                                      |

| input                     |         | ddr4a_avmm_0_reset_n       | Active low reset to user logic. Reset for the user clock domain. Asynchronous assertion and synchronous de-assertion                 |

| input                     |         | ddr4a_avmm_0_waitrequest   | Wait-request is asserted when controller Avalon memory-mapped interface interface is busy                                            |

| input                     | [255:0] | ddr4a_avmm_0_readdata      | Read data from external memory                                                                                                       |

| input                     |         | ddr4a_avmm_0_readdatavalid | Indicates readdata is valid when high                                                                                                |

| output                    | [6:0]   | ddr4a_avmm_0_burstcount    | Number of transfers in each read/write burst                                                                                         |

| output                    | [255:0] | ddr4a_avmm_0_writedata     | AFU supplied data to written to external memory                                                                                      |

| output                    | [25:0]  | ddr4a_avmm_0_address       | Word address forAvalon memory-mapped interface interface of memory controller                                                        |

| output                    |         | ddr4a_avmm_0_write         | Write request from AFU                                                                                                               |

| output                    |         | ddr4a_avmm_0_read          | Read request from AFU                                                                                                                |

| output                    | [31:0]  | ddr4a_avmm_0_byteenable    | Write byte enable from AFU                                                                                                           |

| DDR4A_1 Interface         |         |                            |                                                                                                                                      |

| input                     |         | ddr4a_avmm_1_clk           | Copy of ddr4a_avmm_0_clk                                                                                                             |

| input                     |         | ddr4a_avmm_1_reset_n       | Secondary active low reset to user logic. Reset for<br>the user clock domain. Asynchronous assertion and<br>synchronous de-assertion |

| input                     |         | ddr4a_avmm_1_waitrequest   | Wait-request is asserted when controller Avalon memory-mapped interface interface is busy                                            |

| input                     | [255:0] | ddr4a_avmm_1_readdata      | Read data from external memory                                                                                                       |

| input                     |         | ddr4a_avmm_1_readdatavalid | Indicates readdata is valid when high                                                                                                |

| output                    | [6:0]   | ddr4a_avmm_1_burstcount    | Number of transfers in each read/write burst                                                                                         |

| output                    | [255:0] | ddr4a_avmm_1_writedata     | AFU supplied data to written to external memory                                                                                      |

| output                    | [25:0]  | ddr4a_avmm_1_address       | Word address for Avalon memory-mapped interface interface of memory controller                                                       |

| output                    |         | ddr4a_avmm_1_write         | Write request from AFU                                                                                                               |

| output                    |         | ddr4a_avmm_1_read          | Read request from AFU                                                                                                                |

| output                    | [31:0]  | ddr4a_avmm_1_byteenable    | Write byte enable from AFU                                                                                                           |

You can combine both of the Ping Pong Avalon memory-mapped interface interfaces from one DDR4 bank to form a 512-bit interface with an Avalon combiner. The factory image example demonstrates the use of the Avalon combiner.

The DDR4A and DDR4B interfaces are suited to large record storage, off chip deep packet queues and other storage needs.

## 3.2.4.5.2. DDR4C

| ccip_std_afu<br>Direction | Width   | Signal Name                | Description                                                                                                          |

|---------------------------|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------|

| input                     |         | ddr4c_avmm_0_clk           | 266 MHz clock sourced from EMIF                                                                                      |

| input                     |         | ddr4c_avmm_0_reset_n       | Active low reset to user logic. Reset for the user clock domain. Asynchronous assertion and synchronous de-assertion |

| input                     |         | ddr4c_avmm_0_waitrequest   | Wait-request is asserted when controller Avalon memory-mapped interface interface is busy                            |

| input                     | [127:0] | ddr4c_avmm_0_readdata      | Read data from external memory                                                                                       |

| input                     |         | ddr4c_avmm_0_readdatavalid | Indicates readdata is valid when high                                                                                |

| output                    | [6:0]   | ddr4c_avmm_0_burstcount    | Number of transfers in each read/write burst                                                                         |

| output                    | [127:0] | ddr4c_avmm_0_writedata     | AFU supplied data to written to external memory                                                                      |

| output                    | [25:0]  | ddr4c_avmm_0_address       | Word address for Avalon memory-mapped interface interface of memory controller                                       |

| output                    |         | ddr4c_avmm_0_write         | Write request from AFU                                                                                               |

| output                    |         | ddr4c_avmm_0_read          | Read request from AFU                                                                                                |

| output                    | [15:0]  | ddr4c_avmm_0_byteenable    | Write byte enable from AFU                                                                                           |

The <code>ccip\_std\_afu</code> interfaces to DDR4C by an Avalon memory-mapped interface interface as defined below:

## 3.2.4.5.3. QDR4 Interface

The external QDR4 SRAM is well suited for fast table look ups and external statistics counter storage due to the fast random access capabilities of QDR4 SRAM. QDR4 SRAM transfers 4 data words per clock cycle. QDR4 SRAM also has two independent bidirectional double data rate ports that support concurrent read/write transactions on both ports.

The multiple access ports of the QDR4 SRAM results in the internal interface providing 8 – Avalon memory-mapped interface interfaces for this external memory device. The interface is shown below:

| ccip_std_afu<br>Direction | Width  | Signal Name                  | Description                                                                                                          |

|---------------------------|--------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| input                     |        | qdr_avmm_clk                 | 266 MHz clock sourced from EMIF                                                                                      |

| input                     |        | qdr_avmm_reset_n             | Active low reset to user logic. Reset for the user clock domain. Asynchronous assertion and synchronous de-assertion |

| input                     |        | qdr_avmm_waitrequest [7:0]   | Wait-request is asserted when controller Avalon memory-mapped interface interface is busy                            |

| input                     | [35:0] | qdr_avmm_readdata [7:0]      | Read data from external memory                                                                                       |

| input                     |        | qdr_avmm_readdatavalid [7:0] | Indicates readdata is valid when high                                                                                |

|                           |        |                              | continued                                                                                                            |

| ccip_std_afu<br>Direction | Width  | Signal Name               | Description                                                                    |

|---------------------------|--------|---------------------------|--------------------------------------------------------------------------------|

| output                    | [2:0]  | qdr_avmm_burstcount [7:0] | Number of transfers in each read/write burst                                   |

| output                    | [35:0] | qdr_avmm_writedata [7:0]  | AFU supplied data to written to external memory                                |

| output                    | [21:0] | qdr_avmm_address [7:0]    | Word address for Avalon memory-mapped interface interface of memory controller |

| output                    |        | qdr_avmm_write [7:0]      | Write request from AFU                                                         |

| output                    |        | qdr_avmm_read [7:0]       | Read request from AFU                                                          |

# 3.2.4.6. Ethernet MAC Wrapper Register Access

Host processor access to Ethernet MAC Wrapper is by the CCI-P interface using MMIO indirect access as described in the *FPGA Internal Register Access* section. The RTL modules for register access are included in the encrypted portion of N3000 design and these modules must be included in your design.

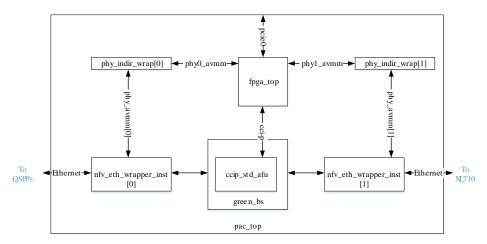

There are two Ethernet MAC Wrappers where one wrapper is connected to the network and the other is connected to the Intel Ethernet Controller XL710-BM2 NIC, as shown below:

## Figure 20. Ethernet Wrapper Register Access

The Ethernet MAC Wrapper registers consist of the following:

- CCI-P required Device Feature Header (DFH) and Information registers are located inside fpga\_top.

- Indirect access control register and status registers are located in phy\_indir\_wrap.

- Ethernet MAC, PHY and multiplex/de-multiplex control and status registers are located in nfv\_eth\_wrapper.

For an example of how software accesses the Ethernet MAC wrapper, see the python source file included with the OPAE software release installation:

inteldevstack/src/opae-\*.\*/usr/tools/extra/fpgadiag/fpgastats.py

The following description of registers below is provided for informational purposes. Do not change or modify this area code, but understanding how this works helps you create your AFU. When the lightweight mode is used, the Ethernet MAC registers are not included.

These registers are organized as follows:

## Table 4. Ethernet MAC Registers

| Register         | Address Offset |

|------------------|----------------|

| ETH_GROUP_0_DFH  | 0x7000         |

| ETH_GROUP_0_INFO | 0x7008         |

| ETH_GROUP_0_CTRL | 0x7010         |

| ETH_GROUP_0_STAT | 0x7018         |

| ETH_GROUP_1_DFH  | 0x8000         |

| ETH_GROUP_1_INFO | 0x8008         |

| ETH_GROUP_1_CTRL | 0x8010         |

| ETH_GROUP_1_STAT | 0x8018         |

The Information register consists of the following fields:

| Table 5. | Information | Register | Fields |

|----------|-------------|----------|--------|

|----------|-------------|----------|--------|

| FIELD NAME            | RANGE   | ACCESS | DEFAULT | DESCRIPTION                                                              |  |

|-----------------------|---------|--------|---------|--------------------------------------------------------------------------|--|

| Reserved              | [63:26] | RsvdZ  | 0x0     | Reserved                                                                 |  |

| MAC light weight mode | [25]    | RO     | 0x0     | 0 - MACs are in normal mode<br>1 - MACs are in light weight mode         |  |

| Direction             | 24      | RO     | 0x0     | 0 – XL710 side<br>1 - Network side                                       |  |

| Speed_Gbs             | [23:16] | RO     | 0xA     | Allowed: 10, 25, 40 Gbs.                                                 |  |

| NofPHYs               | [15:8]  | RO     | 0x8     | Number of PHYs in group                                                  |  |

| GroupID               | [7:0]   | RO     | 0x0     | Unique identifier of phy group. $ETH_GROUP_0 = 0$ ,<br>$ETH_GROUP_1 = 1$ |  |

The indirect control field has one version for 10G mode and a second version for 25G and 40G mode. The 10G mode is shown below:

# Table 6.10G Indirect Control Field

| FIELD NAME    | RANGE   | ACCESS | DEFAULT | DESCRIPTION                                                                                                                                        |     |

|---------------|---------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| command       | [63:62] | RW     | 0x0     | Command:<br>0x0 - NOP<br>0x1 - RD request<br>0x2 - WR request                                                                                      |     |

| reserved      | [61:54] | RO     | 0x0     |                                                                                                                                                    |     |

| device select | [53:49] | RW     | 0x0     | 0x0 - Ethernet Wrapper regs select<br>0x2, 0x4, 0x6, 0x8, 0xA, 0xC, 0xE, 0x10 - PHY select<br>0x3, 0x5, 0x7, 0x9, 0xB, 0xD, 0xF, 0x11 - MAC select |     |

| continued     |         |        |         |                                                                                                                                                    | ued |

| PHY select                            |         |    |     | device select = 0x2, 0x4, 0x6, 0x8, 0xA, 0xC, 0xE, 0x10                                                                                                                                                |

|---------------------------------------|---------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| add features<br>select                | [48]    | RW | 0x0 | 0x0 - phy select<br>0x1 - reset controller / link status select                                                                                                                                        |

| PHY Address/reset<br>ctrl/link status | [47:32] | RW | 0x0 | add features select = 0x0:<br>PHY reconfiguration interface www.altera.com/literature/hb/arria-10/<br>ug_arria10_xcvr_phy.pdf<br>add features select = 0x1: ref. to add features tab.                  |

| MAC register<br>address               | [48:32] | RW | 0x0 | When device select = 0x3, 0x5, 0x7, 0x9, 0xB, 0xD, 0xF, 0x11<br>This field is for Ethernet MAC IP registers as defined in:<br>www.altera.com/en_US/pdfs/literature/ug/<br>ug_32b_10g_ethernet_mac.pdf. |

| ethernet wrapper<br>regs address      | [48:32] |    |     | When device select = 0x0<br>This field includes Ethernet Mux/De-Mux registers                                                                                                                          |

| write data                            | [31:0]  | RW | 0x0 | Write data for phy registers                                                                                                                                                                           |

For 25G and 40G mode:

#### Table 7. 25G and 40G Indirect Control Field

| FIELD NAME                         | RANGE   | ACCESS | DEFAULT | DESCRIPTION                                                                                              |

|------------------------------------|---------|--------|---------|----------------------------------------------------------------------------------------------------------|

| command                            | [63:62] | RW     | 0x0     | Command:<br>0x0 - NOP<br>0x1 - RD request<br>0x2 - WR request                                            |

| reserved                           | [61:54] | RO     | 0x0     |                                                                                                          |

| device select                      | [53:49] | RW     | 0x0     | 0x0 - ethernet wrapper regs select<br>0x2, 0x4, 0x6, 0x8 - PHY select<br>0x3, 0x5, 0x7, 0x9 - MAC select |

| PHY select                         |         |        |         | device select = $0x2$ , $0x4$ , $0x6$ , $0x8$                                                            |

| add features select                | [48]    | RW     | 0x0     | 0x0 - phy select<br>0x1 - reset controller / link status select                                          |

| PHY Address/reset ctrl/link status | [47:32] | RW     | 0x0     | add features select = $0x0$ :<br>add features select = $0x1$ : ref. to add features tab.                 |

| MAC select                         |         |        |         | device select = 0x3, 0x5, 0x7, 0x9                                                                       |

|                                    | [48:32] |        |         |                                                                                                          |

| Ethernet Wrapper regs address      | [48:32] |        |         | When device select = 0x0<br>This field includes Ethernet Mux/De-Mux registers                            |

## **Related Information**

- FPGA Internal Register Access on page 13 ٠

- FPGA Internal Register Access on page 13 ٠

# 3.3. Factory Image Description

The N3000 provides an example design that demonstrates usage of the key interfaces available to the ccip\_std\_afu module.

The block diagram of each network configuration is shown below:

#### EEPROM EEPROM A10 FPGA Eth Wrapper 8x10 Mode Only Eth Wra Ext. Ibk PKVL Av10 AVST UPL AVST CSR Ext. Ibk QSFP FVL 4x1( PKVL **v**8 PCle PCle x 16 edge onnecto PCle x16 Host SW Switch AvMM AvMM PCle Gen3 8x PCle x8 BBS UPL ETH Group PCIe Ibk (NLB) Mem Test (DMA) MUX ETH Group PCle Gen3 8x Ext Mem Status NIOS PKVI/SPI Ctrl PCIe x8 MAC ROM FME Private Features rivate eatures NIOS PKVL SMBus DDR4 DDR4 Ctrlr Ctrlr SPI/QSPI Ctrlr DDR4 Ctrlr QDRIV Ctrlr 120 DDR4 Mem MAC DDR4 ROM Mem DDR4 Mem QDRIV Mem MDIO ► NIOS Flash 120 IRQ A 10 img Flash

# Figure 21. Factory Image Block Diagram for 8x10 GbE

#### Figure 23. Factory Image Block Diagram for 4x25 GbE

The Factory Images include the following high level functions:

- Memory-to-memory DMA blocks illustrating host to and from external memory transfers. For more information about this component, refer to the DMA Accelerator Functional Unit (AFU) User Guide: Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA.

- Native Loopback to test memory reads and writes, bandwidth, and latency. For ٠ more information, refer to the Native Loopback Accelerator Functional Unit (AFU) User Guide.

- Aggregated Ethernet interface

- Required board management functions •

# **Related Information**

- DMA Accelerator Functional Unit (AFU) User Guide: Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA

- Native Loopback Accelerator Functional Unit (AFU) User Guide

# 4. Creating an N3000 FPGA Design

In this section, steps are provided to create your AFU. The following AFU design directories are included:

- hello\_afu this is a simple AFU design illustrating basic design concepts

- Factory\_Image this is a complex AFU design illustrating usage of Ethernet and external memories

- Initial\_Shell\_AFU this design directory serves as the starting point for your AFU. The required project files are included.

In this section, you are referred to these design directories as a way to highlight points in the AFU creation, compilation and running of an application on the N3000. Use these points to create more complex AFU designs for your specific application.

# 4.1. Create New Project Directory

The Initial\_Shell\_AFU provides the starting structure for your AFU design.

Create a new project directory and copy the Initial\_Shell\_AFU files to the new project directory.

\$ mkdir <Your new project directory name> \$ cd <Your new project directory name> \$ cp -R \$N3000\_EXAMPLE\_ROOT/Initial\_Shell\_AFU/\* .

Your design directory is now ready for your new design work.

# 4.2. Create Your AFU Design Files

As a minimum, create the following files for your AFU design:

- 1. ccip\_std\_afu.sv this file is where your AFU connects to CCI-P fabric, external memory and Ethernet

- 2. An AFU file. You can see AFU examples in hello\_afu/hw/afu/hw/rtl/ hello\_afu.sv and Factory\_Image/hw/afu/rtl/afu

- 3. afu.qsf this Intel Quartus Prime file adds your RTL and design files

- 4. afu.sdc this Intel Quartus Prime file specifies your AFU timing constraints

# 4.2.1. ccip\_std\_afu.sv

;

The Initial\_Shell\_AFU includes ccip\_std\_afu.sv starting file where you can instantiate your AFU. Review of this file shows import ccip\_if\_pkg::\* to include definitions of CCI-P interface structures.

```

import ccip_if_pkg::*; //required for CCI-P definitions

module ccip_std_afu #( ....

;

```

There is a CCI-P interface register to improve timing as shown below:

```

// ______

// Register SR <--> PR signals at interface before consuming it

(* noprune *) logic [1:0] pck_cp2af_pwrState_T1;

(* noprune *) logic

pck_cp2af_error_T1;

logic

pck_cp2af_softReset_T1;

t_if_ccip_Rx pck_cp2af_sRx_T1;

t_if_ccip_Tx pck_af2cp_sTx_T0;

pck_af2cp_sTx_T0;

t_if_ccip_Tx

// Register PR <--> PR signals near interface before consuming it

// _____

ccip_interface_reg inst_green_ccip_interface_reg (

.pck_cp2af_softReset_T0

.pClk

(pClk),

(pck_cp2af_softReset),

(pck_cp2af_pwrState),

(pck_cp2af_error),

.pck_cp2af_pwrState_T0

.pck_cp2af_error_T0

.pck_cp2af_sRx_T0

(pck_cp2af_sRx),

.pck_af2cp_sTx_T0

(pck_af2cp_sTx_T0),

.pck_cp2af_softReset_T1 (pck_cp2af_softReset_T1),

.pck_cp2af_pwrState_T1 (pck_cp2af_pwrState_T1),

.pck_cp2af_error_T1 (pck_cp2af_error_T1),

.pck_cp2af_sRx_T1 (pck_cp2af_sRx_T1),

.pck_cp2af_sRx_T1

(pck_cp2af_sRx_T1),

.pck_af2cp_sTx_T1

(pck_af2cp_sTx)

);

```

Your AFU design connects to this registered CCI-P interface.

# 4.2.2. AFU File

Your AFU requires a CCI-P package and a UUID for proper connectivity with host software. See example below:

```

import ccip_if_pkg::*;

module hello_afu

(

input clk, // Core clock. CCI interface is synchronous to this clock.

input reset, // CCI interface ACTIVE HIGH reset.

// CCI-P signals

input t_if_ccip_Rx cp2af_sRxPort,

output t_if_ccip_Tx af2cp_sTxPort

);

`define AFU_ACCEL_UUID 128'h850adcc2_6ceb_4b22_9722_d43375b61c66

// The AFU must respond with its AFU ID in response to MMIO reads of

// the CCI-P device feature header (DFH). The AFU ID is a unique ID

// for a given program. Here we generated one with the "uuidgen"

// program and stored it in the AFU's JSON file. ASE and synthesis

```

```

// setup scripts automatically invoke the OPAE afu_json_mgr script

// to extract the UUID into afu_json_info.vh.

logic [127:0] afu_id = `AFU_ACCEL_UUID;

```

*Note:* For a more complicated example where multiple sub-AFUs are instantiated, refer to Factory\_Image/hw/afu/rtl/afu\_dma.sv.

The software framework and the application software use the AFU\_ID to ensure that they are matched to the correct AFU; that is, that they are obeying the same architectural interface.

The  $AFU_ID$  is a 128-bit value which is generated using an UUID/GUID generator to ensure the value is unique.

For more information about UUID/GUID, refer to the "Online GUID Generator" web page.

#### **Related Information**

Online GUID Generator

#### 4.2.3. **QSF** File

The afu.qsf is where you include your AFU RTL and any other required implementation files. The Intial\_Shell\_AFU includes an afu.qsf file where you can add your specific files.

#### 4.2.4. SDC File

The afu.sdc is where you include your AFU timing constraints files.

#### 4.3. Build with make

The process of creating an N3000 FPGA image is simplified with the provided Makefile that automates the setting of compile parameters and combining your design files with the supplied source files. The Makefile flow starts with your design input files and ends after Intel Quartus Prime synthesizes and places the output and a binary FPGA file that is ready for secure signing with PACSign.

The make flow is only supported on  ${\sf Linux}^*$  platforms. Your development system requires the following:

#### Make:

make 3.81 (or newer)

#### Python:

Python 3.6

You invoke the make flow with the following command input syntax:

make [target] [options] [paths] [versioning]

**Target**—required, input only one:

# intel

- 2x1x25G

- 2x2x25G

- 4x25G

- 8x10G

- 2x1x25Gx2FVL

- 1x2x25G

- clean

- archive

Target archive stores whole database as a Quartus Archive (.qar) file.

#### Options

| Option              | Value           | Description                            | Required | Default        | Comment                                                                             |

|---------------------|-----------------|----------------------------------------|----------|----------------|-------------------------------------------------------------------------------------|

| GUI                 | 0               | run selected stage                     | NO       | 0              |                                                                                     |

|                     | 1               | open Intel Quartus<br>Prime GUI        |          |                |                                                                                     |

| SEED                | 0 - 232-1       | fitter seed                            | NO       | 1              | Helpful in achieving timing closure                                                 |

| STAGE               | compile         | execute full flow<br>(step-by-step)    | YES      | Not applicable |                                                                                     |

|                     | synthesis       | execute analysis and synthesis         |          |                | calls ipgenerate                                                                    |

|                     | fitter          | execute fitting (Fit,<br>Place, Route) |          |                | calls ipgenerate                                                                    |

|                     | fitter-timing   | execute fitter and timing analysis     |          |                | calls ipgenerate                                                                    |

|                     | analysis-timing | execute timing<br>analysis             |          |                | requires completed fitter                                                           |

|                     | analysis-power  | execute power<br>analysis              |          |                | requires completed fitter                                                           |

|                     | assembler       | execute assembler                      |          |                | requires completed fitter                                                           |

|                     | ipgenerate      | generate IPs                           |          |                |                                                                                     |

|                     | dummy           | do nothing                             |          |                | GUI only                                                                            |

| USE_BBS_CLK         | 0               | do not take user clock<br>from BBS     | NO       | 0              |                                                                                     |

|                     | 1               | take user clock from<br>BBS            |          |                | Required if CCI-P<br>clock uClk_usr or<br>uClk_usrDiv2 is<br>used in your<br>design |

| INCLUDE_DIAGNOSTICS | 0               | exclude AFU<br>diagnostics             | NO       | 1              |                                                                                     |

|                     | 1               | include AFU<br>diagnostics             |          |                |                                                                                     |

| INCLUDE_AFU_PCIE1   | 0               | exclude AFU PCIe1                      | NO       | 1              |                                                                                     |

|                     |                 | I                                      | J        | I              | continued                                                                           |

#### 4. Creating an N3000 FPGA Design 683190 | 2022.07.15

## intel

| Option               | Value         | Description                           | Required | Default        | Comment                              |

|----------------------|---------------|---------------------------------------|----------|----------------|--------------------------------------|

|                      | 1             | include AFU PCIe1                     |          |                |                                      |

| INCLUDE_MEMORY       | 0             | exclude all EMIFs                     | NO       | 1              |                                      |

|                      | 1             | include all EMIFs                     | ]        |                |                                      |

| INCLUDE_DDR4_A       | 0             | exclude DDR4 A                        | NO       | INCLUDE_MEMORY |                                      |

|                      | 1             | include DDR4 A                        |          |                |                                      |

| INCLUDE_DDR4_B       | 0             | exclude DDR4 B                        | NO       | INCLUDE_MEMORY |                                      |

|                      | 1             | include DDR4 B                        |          |                |                                      |

| INCLUDE_DDR4_C       | 0             | exclude DDR4 C                        | NO       | INCLUDE_MEMORY |                                      |

|                      | 1             | include DDR4 C                        |          |                |                                      |

| INCLUDE_QDR          | 0             | exclude QDR                           | NO       | INCLUDE_MEMORY |                                      |

|                      | 1             | include QDR                           |          |                |                                      |

| MAC_LIGHTWEIGHT_MODE | 0             | disabled                              | NO       | 0              | Disabled non<br>required features in |

|                      | 1             | enabled                               |          |                | MACs for less logic<br>consumption   |

| DATAPATH_MODE        | normal        | Ethernet aggregated mode              | NO       | normal         |                                      |

|                      | disaggregated | disaggregated<br>Ethernet mode        |          |                |                                      |

|                      | lightweight   | lightweight Ethernet<br>mode          |          |                |                                      |

| INCLUDE_SEU          | 0             | Excludes SEU<br>detection circuit     | NO       | 1              |                                      |

|                      | 1             | Includes SEU<br>detection circuit     |          |                |                                      |

| ARCHIVE_NAME         | [any string]  | .gar archive name<br>for .gdb archive | NO       | snapshot.qar   | used by archive<br>target            |

Usage Examples:

1. Set up your shell environment to use N3000 provided Intel Quartus Prime

\$ source <N3000 Installation Directory>/inteldevstack/bin/init\_env.sh

The example of the N3000 Make command runs the full compile process of the 2 x 2 x 25 GbE factory image using the command line (non-GUI) mode with fitter seed equal to 5:

\$ make 2x2x25G SEED=5 STAGE=compile

*Note:* Some designs may require multiple seed passes using seeds 1 to 8 to achieve timing closure. Also, the Design Space Explorer does not work with the N3000 make design flow.

Send Feedback

#### Paths

| Path         | Description                                          | Default                   |

|--------------|------------------------------------------------------|---------------------------|

| PROJECT_FILE | main project qpf                                     | prj/pac_baseline/chip.qpf |

| PAC_ROOT     | N3000 sources root where main .qip is located        | hw/pac                    |

| AFU_ROOT     | AFU sources root where $\mathtt{afu.qsf}$ is located | hw/afu/hw                 |

#### Versioning

| Versioning      | Description           | Default |

|-----------------|-----------------------|---------|

| PAC_VER_MAJOR   | SemVer Major. 0 - 15  | 0       |

| PAC_VER_MINOR   | SemVer Minor. 0 – 255 | 0       |

| PAC_VER_PATCH   | SemVer Patch. 0 – 15  | 0       |

| REVISION_ID     | 32-bit                | 0       |

| AFU_REVISION_ID | 12-bit                | 0       |

#### Pr\_Interface\_ID

The OPAE tool fpgainfo lists the target configuration unique Pr\_Interface\_ID:

| TARGET  | Pr_Interface_ID                      |  |  |

|---------|--------------------------------------|--|--|

| 8x10G   | 901DD697-CA79-4B05-B843-8138CEFA2846 |  |  |

| 4x25G   | F3C99413-5081-4AAD-BCED-07EB84A6D0BB |  |  |

| 2x2x25G | A5D72A3C-C8B0-4939-912C-F715E5DC10CA |  |  |

The build process combines your <code>afu.qsf</code> file with a top level <code>chip.qsf</code> that includes external memory interfaces, MACs, and the encrypted CCI-P and management blocks.

To compile the  $hello_afu$  targeting the 2x2x25 network interface, execute the following in the top directory:

```

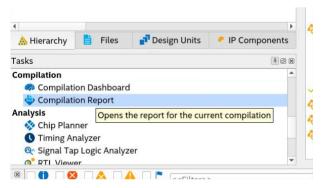

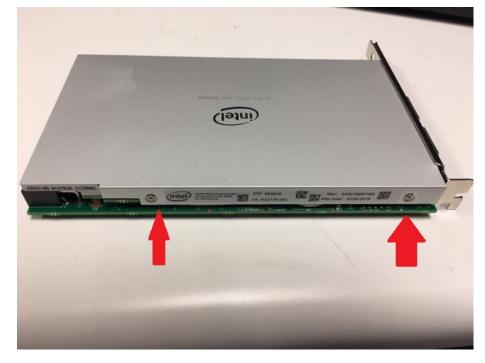

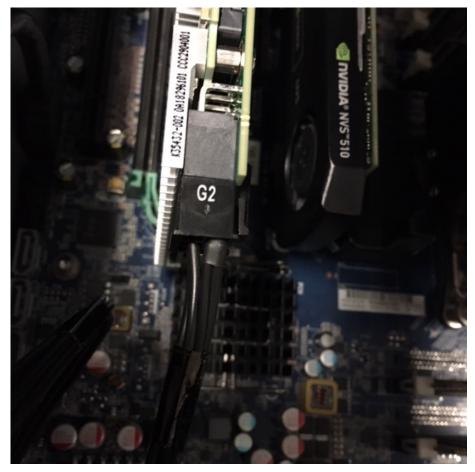

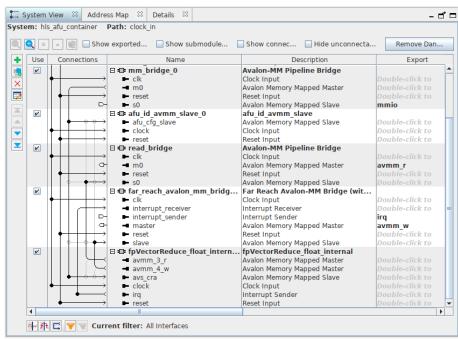

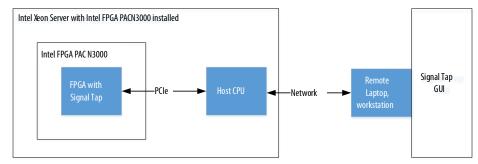

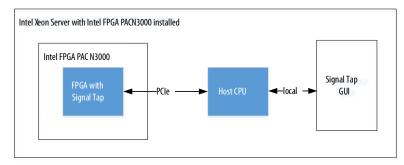

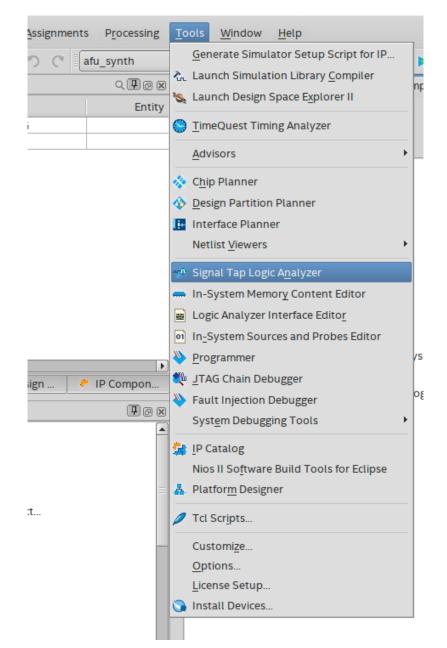

$ cd $N3000_EXAMPLE_ROOT/hello_afu